ispLSI

®

2128VE

3.3v 在系统内 可编程

superfast™ 高 密度 pld

2128ve_08

1

特点

• superfast 高 密度 在系统内

可编程 逻辑

— 6000 pld 盖茨

— 128 和 64 我/o 管脚 版本, 八 专用 输入

— 128 寄存器

— 高 速度 全球 互连

— 宽 输入 浇口 用于 快 计数器, 州

机器, 地址 解码器, 等

— 小 逻辑 块 尺寸 用于 随机 逻辑

— 100% 功能, 电子元件工业联合会 和 引出线 兼容

与 isplsi 2128v 设备

• 3.3v 低 电压 2128 体系结构

— 接口 与 标准 5v ttl 设备

• 高 业绩 e?

2

CMOS

®

技术

—

f

最大值

= 250mhz 最大值 操作 频率

—

t

pd

= 4.0ns 传播 延迟

— 电气 可擦除 和 可重新编程

— 非挥发性

— 100% 已测试 在 时间 的 制造

— 未使用 产品 期限 停机 保存 电源

• 在系统内 可编程

— 3.3v 在系统内 可编程性 (isp™) 使用

边界 扫描 测试一下 访问权限 港口 (轻敲)

— 开漏极 输出 选项 用于 灵活 总线 接口

能力, 允许 容易 实施 的 有线-

或 总线 仲裁 逻辑

— 增加 制造业 收益率, 减少 时间-至-

市场 和 改进 产品 质量

— 重新编程 焊接 设备 用于 更快 原型设计

• 100% ieee 1149.1 边界 扫描 可测试

• 这 轻松 的 使用 和 快 系统 速度 的

plds 与 这 密度 和 灵活性 的 fpgas

— 增强型 管脚 锁定 能力

— 三个 专用 时钟 输入 针脚

— 同步 和 异步 时钟

— 可编程 输出 回转 费率 控制

— 灵活 管脚 放置位置

— 优化 全球 路由 游泳池 提供 全球

Interconnectivity

• ispdesignexpert™ – 逻辑 编译器 和 com-

完整 isp 设备 设计 系统 从 hdl

合成 通过 在系统内 编程

— 上级 质量 的 结果

— 紧紧地 综合 与 领先 cae 供应商 工具

— productivity 增强 计时 分析仪, explore

工具, 计时 模拟器 和 ispanalyzer™

— pc 和 unix platforms

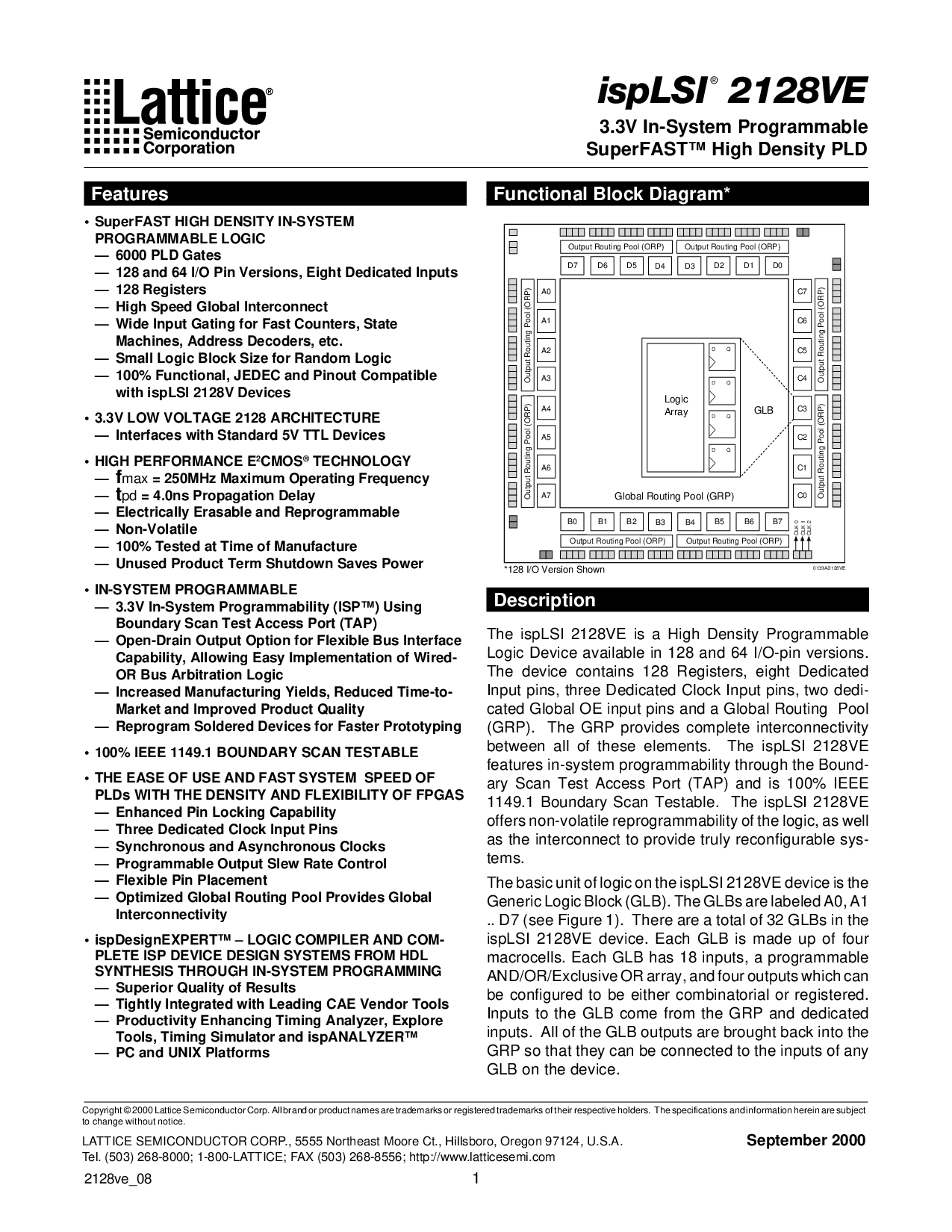

功能 块 diagram*

描述

这 isplsi 2128ve 是 一个 高 密度 可编程

逻辑 设备 可用 入点 128 和 64 我/o-管脚 版本.

这 设备 包含 128 寄存器, 八 专用

输入 针脚, 三个 专用 时钟 输入 针脚, 两个 dedi-

已确定 全球 oe 输入 针脚 和 一个 全球 路由 游泳池

(grp). 这 grp 提供 完成 interconnectivity

之间 全部 的 这些 元素. 这 isplsi 2128ve

特点 在系统内 可编程性 通过 这 已绑定-

ary 扫描 测试一下 访问权限 港口 (轻敲) 和 是 100% ieee

1149.1 边界 扫描 可测试. 这 isplsi 2128ve

优惠 非挥发性 可重新编程性 的 这 逻辑, 作为 井

作为 这 互连 至 提供 真的 可重构 系统-

临时.

这 基本 单位 的 逻辑 开启 这 isplsi 2128ve 设备 是 这

通用 逻辑 块 (glb). 这 glbs 是 已标记 a0, a1

.. d7 (请参见 图 1). 那里 是 一个 合计 的 32 glbs 入点 这

isplsi 2128ve 设备. 每个 glb 是 制造 向上 的 四

宏单元. 每个 glb 有 18 输入, 一个 可编程

和/或/独占 或 阵列, 和 四 产出 哪个 可以

是 已配置 至 是 要么 组合 或 已注册.

输入 至 这 glb 来 从 这 grp 和 专用

输入. 全部 的 这 glb 产出 是 带来了 背面 进入 这

grp 所以 那 他们 可以 是 已连接 至 这 输入 的 任何

glb 开启 这 设备.

全球 路由 游泳池 (grp)

输出 路由 游泳池 (orp) 输出 路由 游泳池 (orp)

输出 路由 游泳池 (orp) 输出 路由 游泳池 (orp)

输出 路由 游泳池 (orp) 输出 路由 游泳池 (orp)

clk 0

输出 路由 游泳池 (orp) 输出 路由 游泳池 (orp)

clk 1

clk 2

逻辑

阵列

GLB

DQ

DQ

DQ

DQ

0139a/2128ve

C7

C6

C5

C4

C3

C2

C1

C0

D3

D2

D1

D0

D7

D6

D5

D4

B4

B5

B6

B7

B0

B1

B2

B3

A0

A1

A2

A3

A4

A5

A6

A7

*128 我/o 版本 显示

版权 © 2000 lattice 半导体 corp. 全部 品牌 或 产品 姓名 是 商标 或 已注册 商标 的 他们的 各自 持有人. 这 规格 和 信息 此处 是 主题

至 变更 无 通知.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

九月 2000

电话. (503) 268-8000; 1-800-lattice; 传真 (503) 268-8556; http://www.latticesemi.com