1

描述

这 cat5401 是 四 digitally 可编程序的

电位器 (dpps™) 整体的 和 控制 逻辑

和 16 字节 的 nvram 记忆. 各自 dpp 组成 的

一个 序列 的 63 resistive elements 连接 在 二

externally accessible 终止 点. 这 tap 点 在

各自 resistive 元素 是 连接 至 这 wiper 输出

和 cmos switches. 一个 独立的 6-位 控制 寄存器

(wcr) independently 控制 这 wiper tap switches 为

各自 dpp. 有关联的 和 各自 wiper 控制 寄存器

是 四 6-位 非-易变的 记忆 数据 寄存器 (dr)

使用 为 storing 向上 至 四 wiper settings. writing 至 这

CAT5401

四方形 Digitally 可编程序的 电位器 (dpp™)

和 64 taps 和 spi 接口

特性

■

四 直线的-taper digitally 可编程序的

电位器

■

64 电阻 taps 每 分压器

■

终止 至 终止 阻抗 2.5k

Ω

, 10k

Ω

, 50k

Ω

或者 100k

Ω

■

分压器 控制 和 记忆 进入 通过

spi 接口: 模式 (0, 0) 和 (1, 1)

■

低 wiper 阻抗, 典型地 80

ΩΩ

ΩΩ

Ω

■

nonvolatile 记忆 存储 为 向上 至 四 wiper

settings 为 各自 分压器

■

自动 recall 的 saved wiper settings 在

电源 向上

■

2.5 至 6.0 volt 运作

■

备用物品 电流 较少 比 1

µ

一个

■

1,000,000 nonvolatile 写 循环

■

100 年 nonvolatile 记忆 数据 保持

■

24-含铅的 soic, 24-含铅的 tssop 和 bga

■

工业的 温度 范围

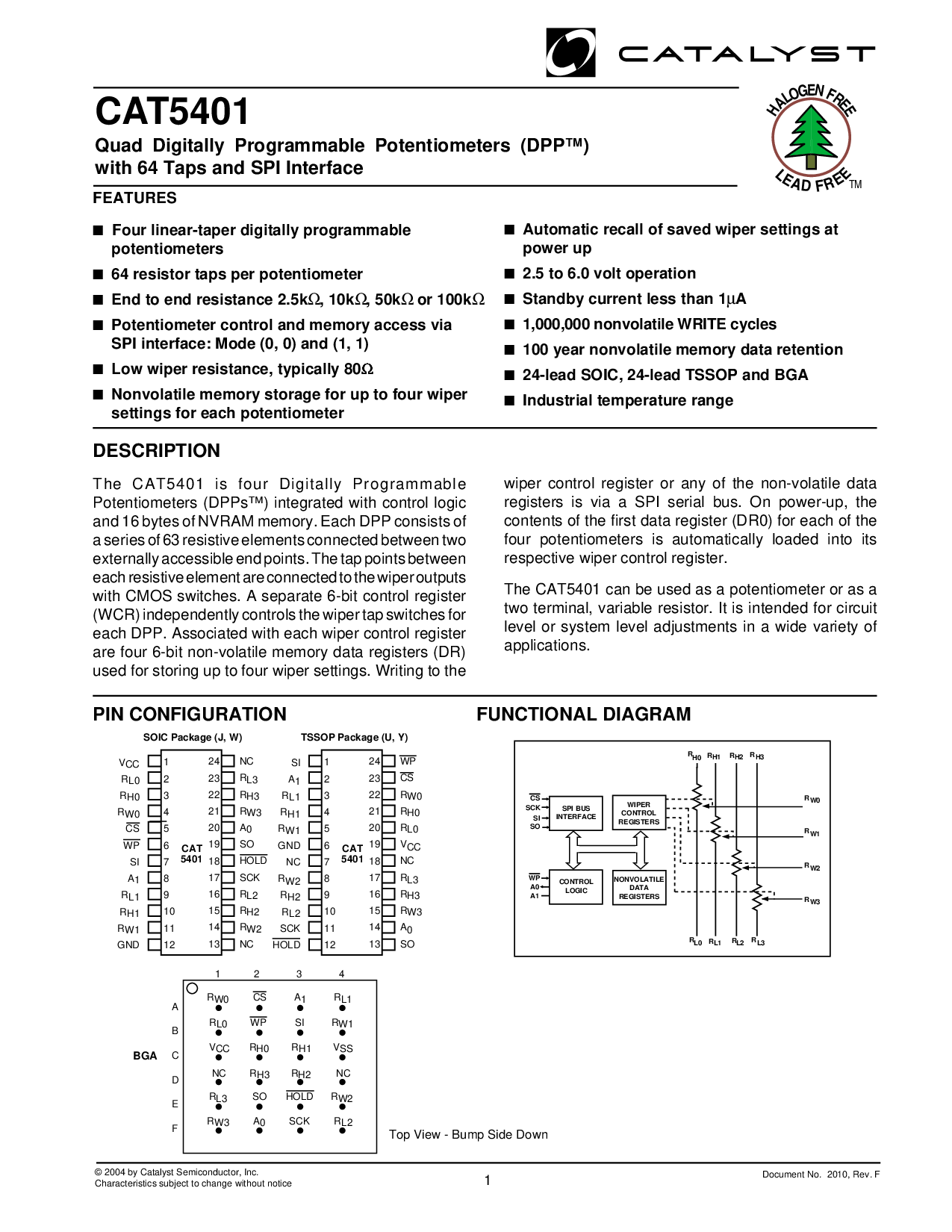

管脚 配置

函数的 图解

© 2004 用 catalyst 半导体, 公司

特性 主题 至 改变 没有 注意

文档 非. 2010, rev. f

wiper 控制 寄存器 或者 任何 的 这 非-易变的 数据

寄存器 是 通过 一个 spi 串行 总线. 在 电源-向上, 这

内容 的 这 第一 数据 寄存器 (dr0) 为 各自 的 这

四 电位器 是 automatically 承载 在 它的

各自的 wiper 控制 寄存器.

这 cat5401 能 是 使用 作 一个 分压器 或者 作 一个

二 终端, 能变的 电阻. 它 是 将 为 电路

水平的 或者 系统 水平的 adjustments 在 一个 宽 多样性 的

产品.

BGA

顶 视图 - bump 一侧 向下

R

H0

W0

W2

W3

W1

H1

H2

H3

R

R

R

R

L0

L1

L2

L3

R

R

R

WIPER

控制

寄存器

NONVOLATILE

数据

寄存器

spi 总线

接口

控制

逻辑

SCK

SI

WP

A0

A1

R

R

R

R

CS

所以

H

一个

L

O

G

E

N

F

R

E

E

TM

L

E

一个

D

F

R

E

E

1 2 3 4

一个

B

C

D

E

F

R

W0

CS 一个

1

R

L1

R

L0

WP SI R

W1

V

CC

R

H0

R

H1

V

SS

NC R

H3

R

H2

NC

R

L3

所以 支撑 R

W2

R

W3

一个

0

SCK R

L2

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

CAT

5401

V

CC

R

L0

R

H0

R

W0

CS

WP

SI

一个

1

R

L1

R

H1

R

W1

地

NC

R

L3

R

H3

R

W3

一个

0

所以

支撑

SCK

R

L2

R

H2

R

W2

NC

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

CAT

5401

SI

一个

1

R

L1

R

H1

R

W1

地

NC

R

W2

R

H2

R

L2

SCK

支撑

WP

CS

R

W0

R

H0

R

L0

V

CC

NC

R

L3

R

H3

R

W3

一个

0

所以

soic 包装 (j, w) tssop 包装 (u, y)