技术类 数据

1

积分

十六进制 d-类型 翻转-翻牌圈 与 重置; 正 边缘-触发器

这 74lv174 是 一个 低–电压 si–闸门 cmos 设备 和 是 管脚 一个钕

功能 兼容 与 这 74hc/hct174.

这 74lv174 有 六个 边缘–已触发 d–类型 翻转–拖鞋 与 个人 d

输入 和 q 产出. 这 普通 时钟 (cp) 和 主人 重置 (mr)

输入 荷载 和 重置 (清除) 全部 翻转–拖鞋 同时.

这 注册是 完全 边缘–已触发. 这 州 的 每个 d 输入, 一个 设置–

向上 时间 之前 至 这 低–至–高 时钟 过渡, 是 已转移 至 这

相应的 输出 的 这 翻转–翻牌圈.

一个 低 水平 开启 这 mr 输入 力 全部 产出 低, 独立 的

时钟 或 数据输入.

这 设备 是 有用的 用于 应用程序 要求 真 产出 仅 和

时钟 和 主人 重置 输入 那 是 普通 至 全部 存储 元素.

•

输出 电压 级别 是 兼容 与 输入 级别 的 cmos,

nmos 和 ttl 集成电路

s

•

供应 电压 范围: 1.2 至 5.5v

•

低 输入 电流: 1.0

µ

À; 0.1

µ

À 在 Ò = 25

°

Ñ

•

输出电流:6ma 在vcc = 3.0v;12 ma 在vcc = 4.5v

•

高 噪声 免疫 特性 的 cmos 设备

IN74LV174

订购 信息

in74lv174n 塑料

in74lv174d soic

iz74lv174 芯片

t

一个

=-40

°

至 125

°

c 用于 全部 软件包

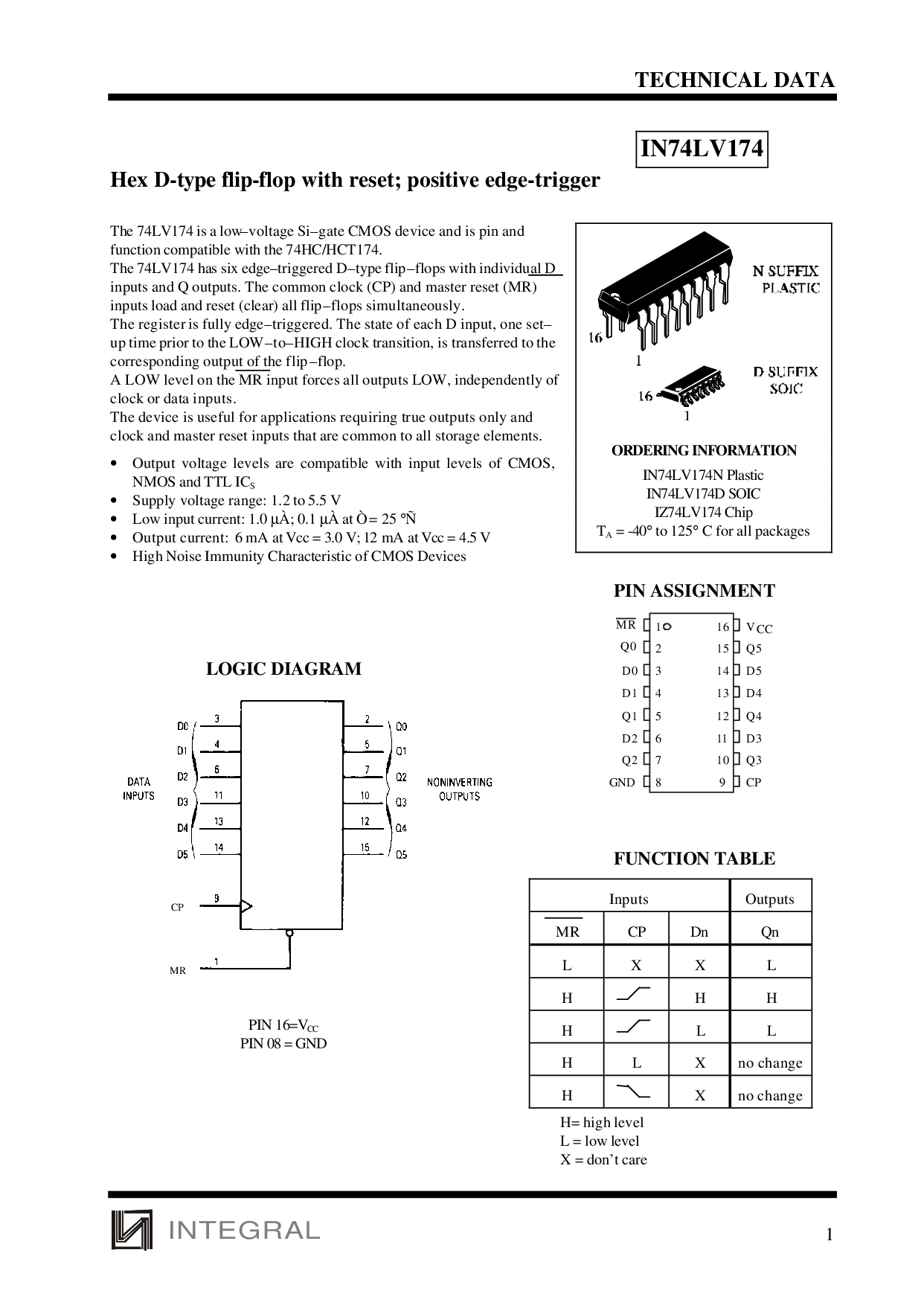

功能 表

输入 产出

MR cp Dn Qn

l x x l

h h h

h l l

h l x 否 ch安吉

h x 否 变更

h= 高 水平

l = 低 水平

x = 唐’t 护理

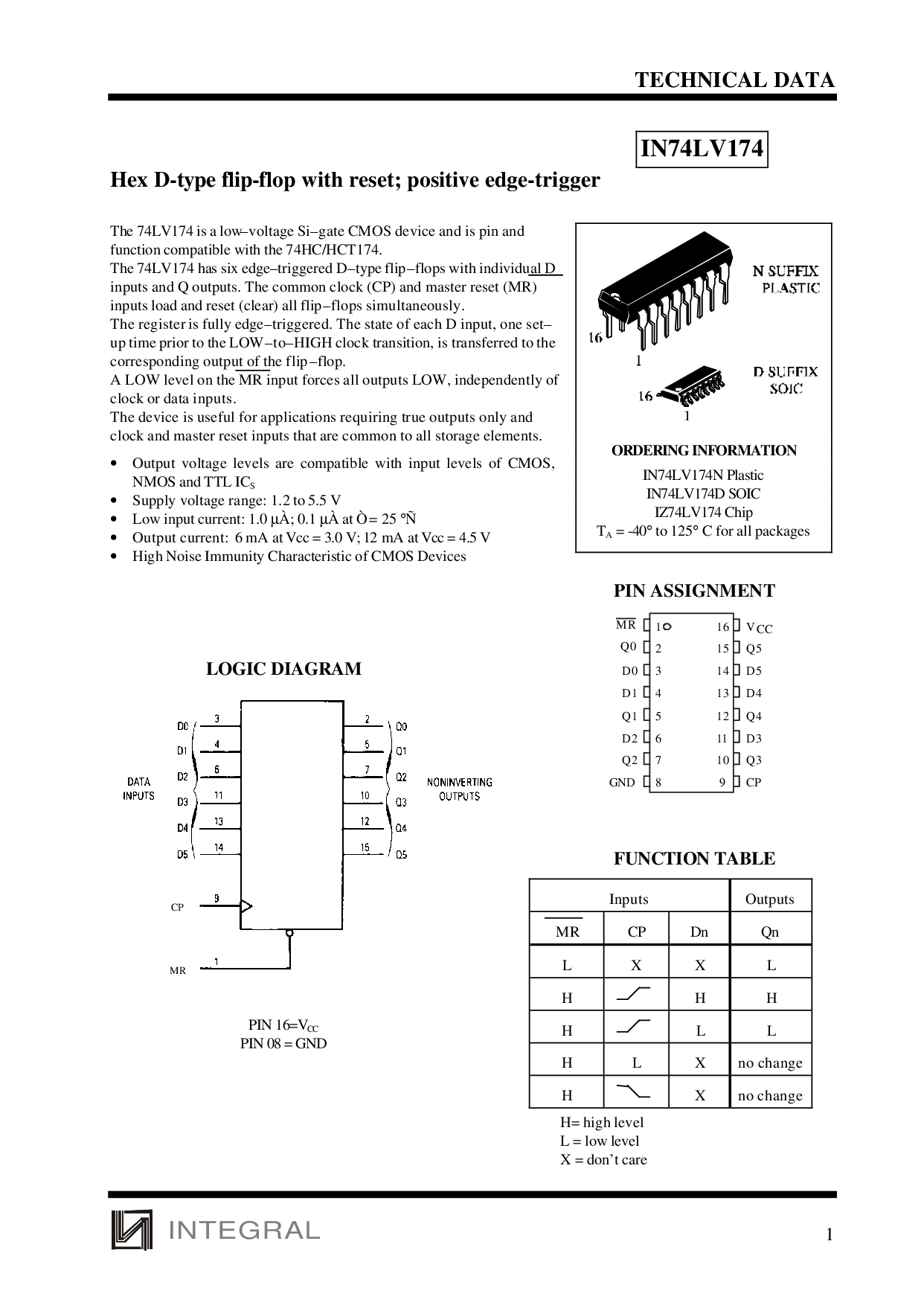

逻辑 图表

管脚 16=v

抄送

管脚 08 = 地

管脚 分配

1

2

3

5

4

6

7

8地

16

15

14

13

12

11

10

9

v

抄送

MR

Q0

D0

D1

Q1

D2

Q2

D5

D4

Q4

D3

Q3

cp

Q5

MR

cp