技术类 数据

1

3-至-8-线 解码器/多路分解器

这个 肖特基-夹紧 ttl msi 电路 是 设计 至 是 已使用 入点

高性能 记忆-decording 或 数据-路由 应用程序

要求 很 短 传播 延迟 时间. 入点 高性能

记忆 系统 这个 解码 可以 是 已使用 至 最小化 这 效果 的

系统 解码. 当 就业 与 高速 回忆 利用

一个 快 启用 电路 这 延迟 次 的 这个 decorder 和 这 启用

时间 的 这 记忆 是 通常 较少 比 这 典型 访问权限 次 的 这

记忆. 这个 手段 那 这 有效 系统 延迟 介绍 由 这

肖特基-clampled 系统 解码器 是 可忽略不计.

•

设计 具体而言 用于 高 速度 记忆 解码器 和 数据

变速器 系统

•

合并 3 enabler 输入 至 简化 层叠 和/或 数据

接待处

•

肖特基 夹紧 用于 高 业绩

IN74LS138

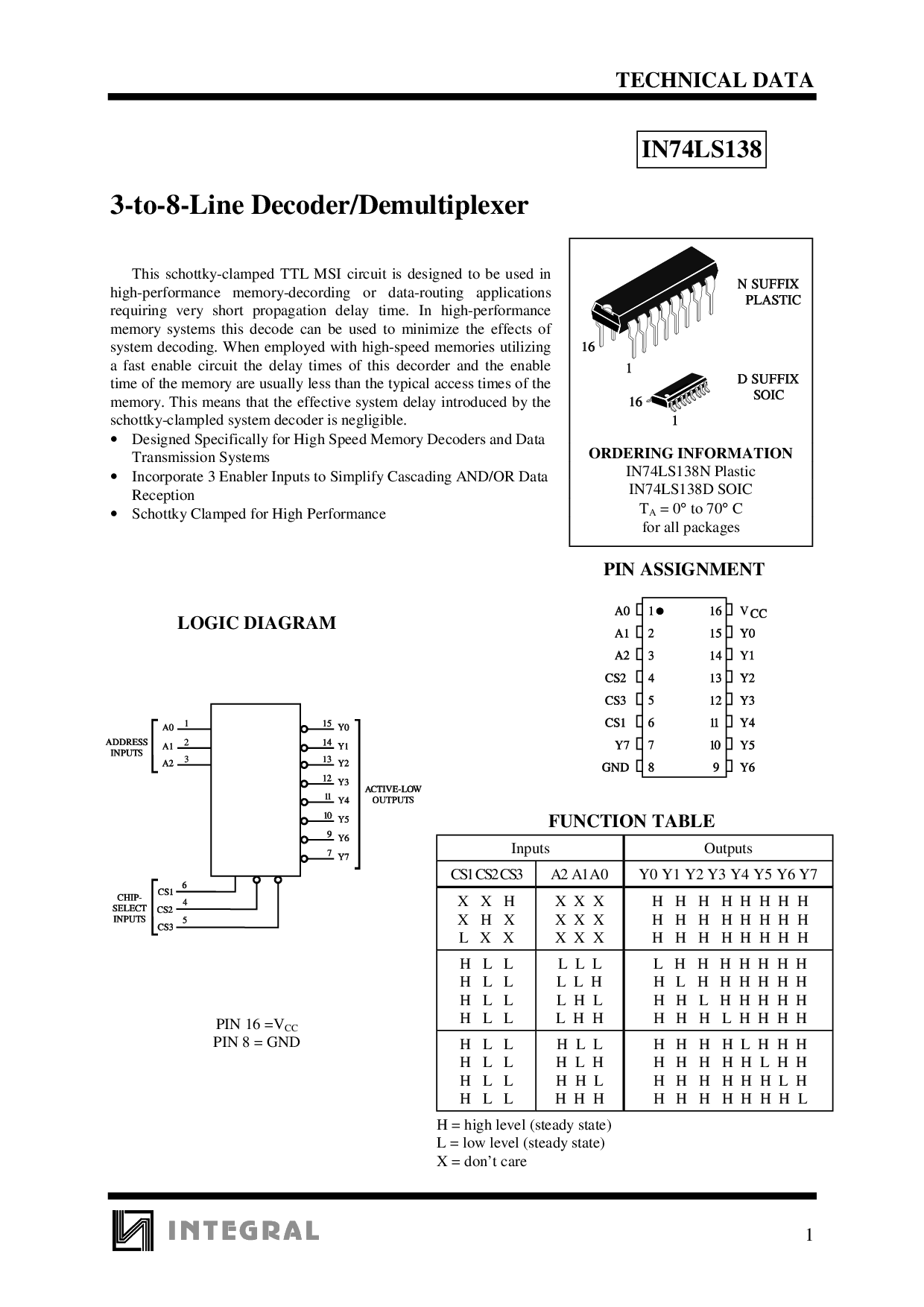

订购 信息

in74ls138n 塑料

in74ls138d soic

t

一个

= 0

°

至 70

°

c

用于 全部 软件包

管脚 分配

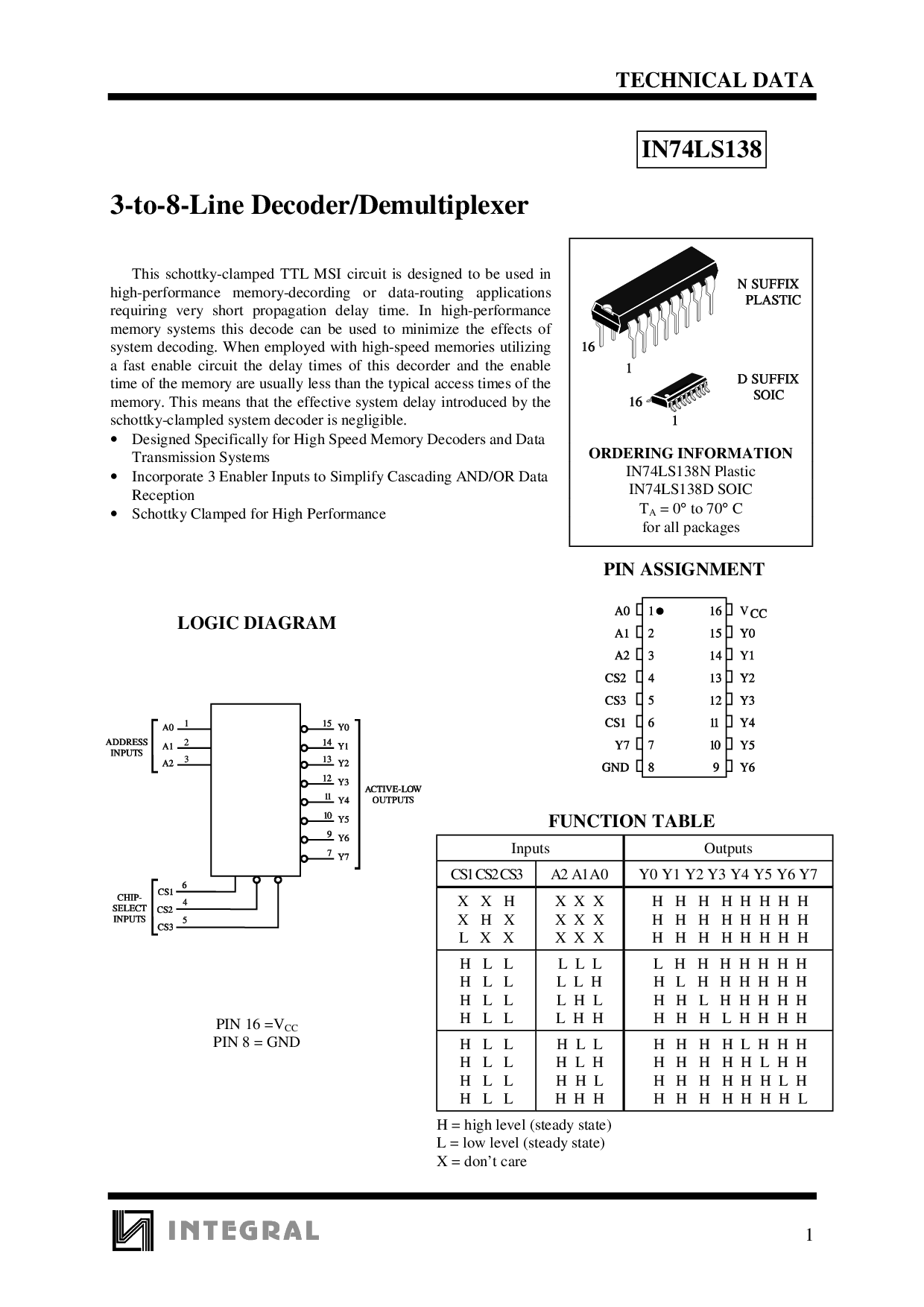

功能 表

输入 产出

cs1 cs2 cs3 a2 a1 a0 y0 y1 y2 y3 y4 y5 y6 y7

x x h

x h x

l x x

x x x

x x x

x x x

h h h h h h h h

h h h h h h h h

h h h h h h h h

h l l

h l l

h l l

h l l

l l l

l l h

l h l

l h h

l h h h h h h h

h l h h h h h h

h h l h h h h h

h h h l h h h h

h l l

h l l

h l l

h l l

h l l

h l h

h h l

h h h

h h h h l h h h

h h h h h l h h

h h h h h h l h

h h h h h h h l

h = 高 水平 (稳定 州)

l = 低 水平 (稳定 州)

x = 唐’t 护理

逻辑 图表

管脚 16 =v

抄送

管脚 8 = 地