规格

ispGAL22V10

1

• 在系统内 programmable™ (5-v 仅)

— 4-电线 串行 编程 接口

— 最小值 10,000 程序/擦除 循环次数

— 内置 下拉 开启 sdi 管脚 消除 离散

电阻 开启 板 (ispgal22v10c 仅)

• 高 业绩 e?

2

CMOS

®

技术

— 7.5 ns 最大值 传播 延迟

— fmax = 111 mhz

— 5 ns 最大值 从 时钟 输入 至 数据 输出

— UltraMOS

®

高级 cmos 技术

• 活动 引体向上 开启 全部 逻辑 输入 和 我/o 针脚

• 兼容 与 标准 22v10 设备

— 完全 功能/保险丝-地图/参数化 兼容

与 双极性 和 cmos 22v10 设备

•E

2

细胞 技术

— 在系统内 可编程 逻辑

— 100% 已测试/100% 收益率

— 高 速度 电气 擦除 (&指示灯;100ms)

— 20 年份 数据 保留

• 十 输出 逻辑 宏单元

— 最大值 灵活性 用于 复杂 逻辑 设计

• 应用程序 包括:

— dma 控制

— 州 机器 控制

— 高 速度 图形 加工

— 软件-驱动 硬件 配置

• 电子 签名 用于 标识

描述

这 ispgal22v10, 在 7.5ns 最大值 传播 延迟 时间,

联合收割机 一个 高 业绩 cmos 流程 与 电气

可擦除 (e?

2

) 浮动 闸门 技术 至 提供 这 行业's

第一 在系统内 可编程 22v10 设备. e?

2

技术 的-

fers 高 速度 (&指示灯;100ms) 擦除 次, 提供 这 能力 至 re-

程序 或 重新配置 这 设备 快速 和 高效.

这 通用 体系结构 提供 最大值 设计 灵活性 由

允许 这 输出 逻辑 宏单元 (olmc) 至 是 已配置 由

这 用户. 这 ispgal22v10 是 完全 功能/保险丝 地图/参数化

兼容 与 标准 双极性 和 cmos 22v10 设备. 这

标准 plcc 包装 提供 这 相同 功能 引出线 作为

这 标准 22v10 plcc 包装 与 no-连接 针脚 正在

已使用 用于 这 isp 接口 信号.

独一无二 测试一下 电路 和 可重新编程 细胞 允许 完成

交流电, 直流, 和 功能 测试 期间 制造. 作为 一个 结果,

lattice 半导体 交付 100% 字段 可编程性 和

功能 的 全部 gal 产品. 入点 加法, 10,000 擦除/写

循环次数 和 数据 保留 入点 超额 的 20 年 是 指定.

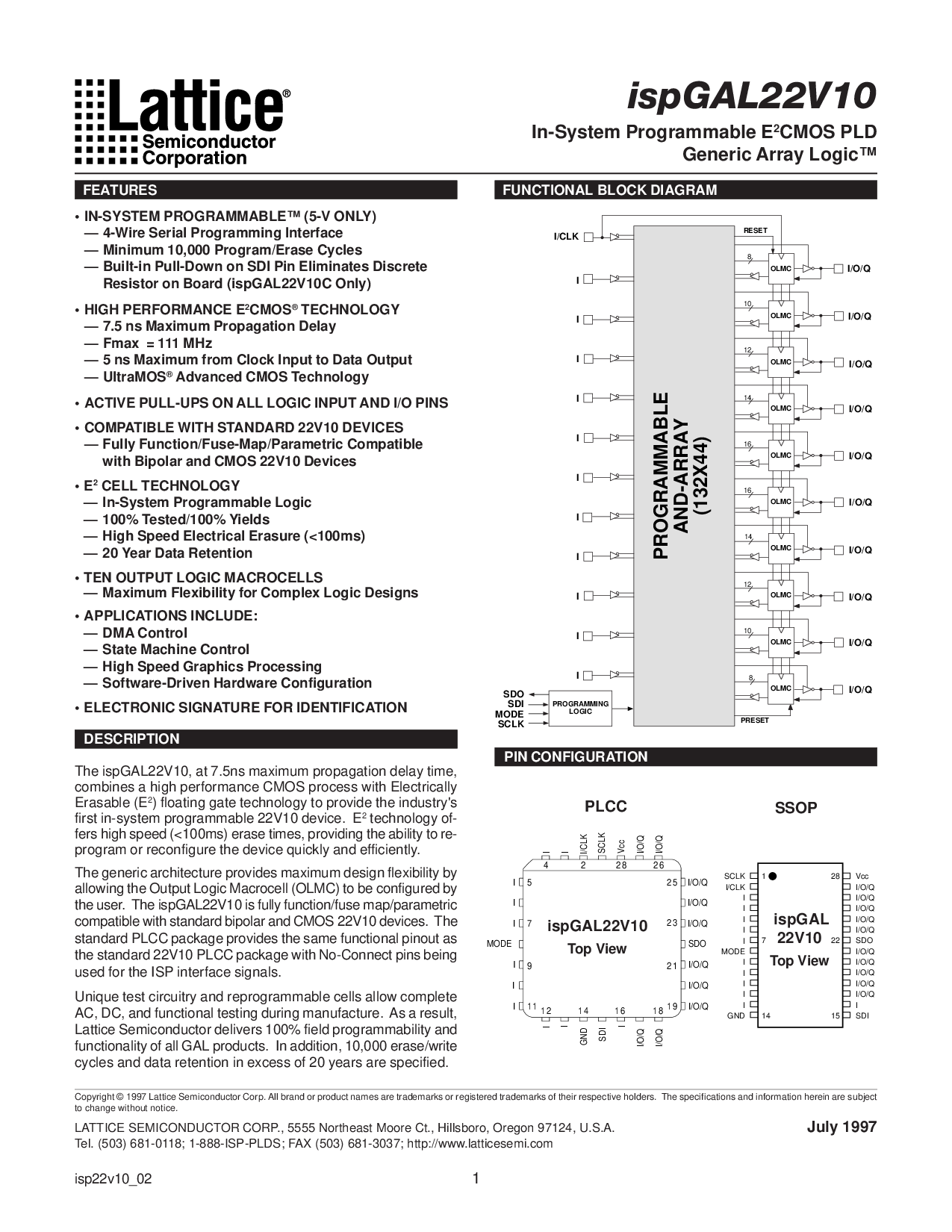

功能 块 图表特点

管脚 配置

可编程

和-阵列

(132x44)

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

SDO

SDI

模式

SCLK

我/clk

我

我

我

我

我

我

我

我

我

我

重置

预置

8

10

12

14

16

16

14

12

10

8

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

编程

逻辑

我

ispGAL22V10

在系统内 可编程 e?

2

cmos pld

通用 阵列Logic™

版权 © 1997 lattice 半导体 corp. 全部 品牌 或 产品 姓名 是 商标 或 已注册 商标 的 他们的 各自 持有人. 这 规格 和 信息 此处 是 主题

至 变更 无 通知.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

july 1997

电话. (503) 681-0118; 1-888-isp-plds; 传真 (503) 681-3037; http://www.latticesemi.com

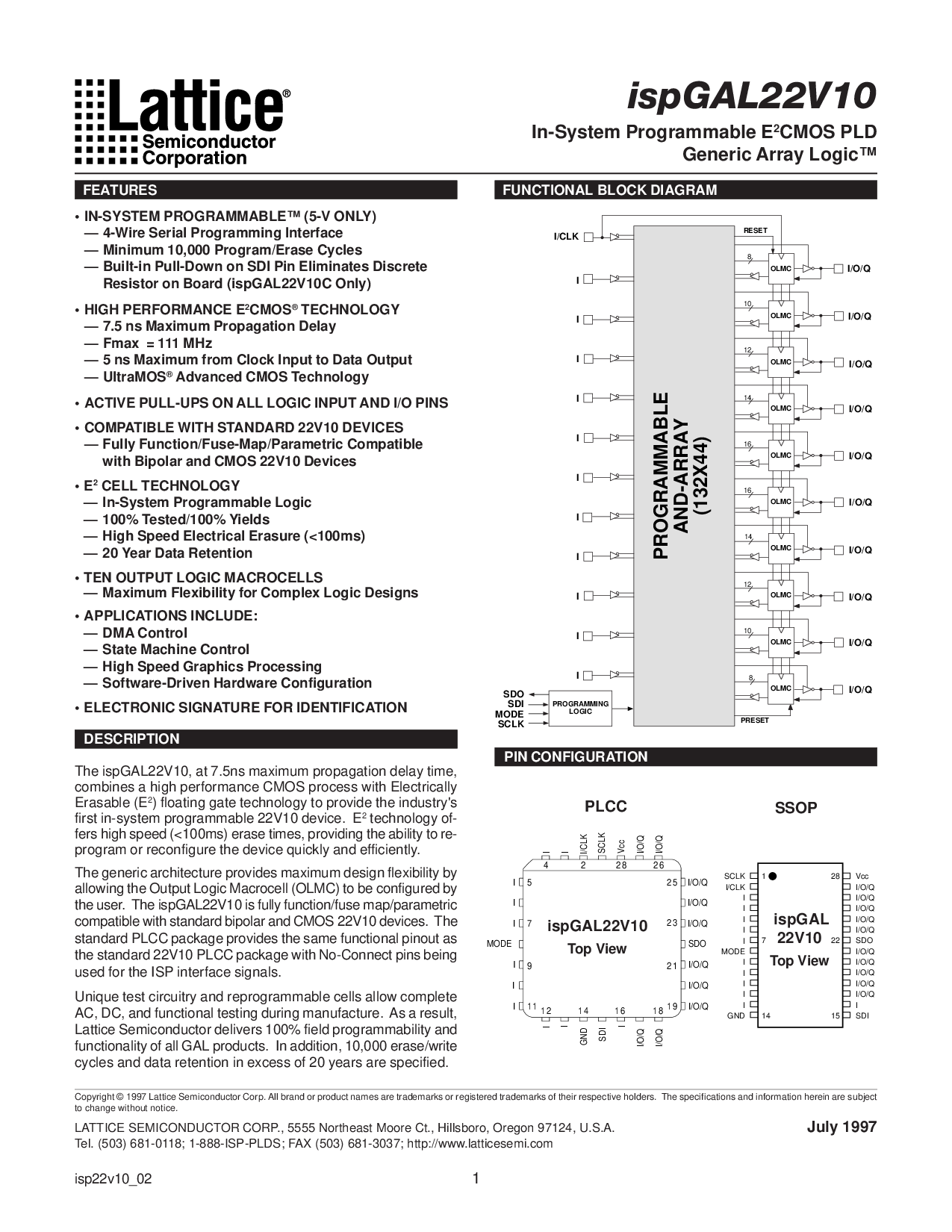

PLCC

SDO

我/o/q

我/o/q

我/o/q

228

我

我

模式

我

我

我

5

11

14 16

19

25

4

7

9

12 18

21

23

26

我

我/o/q

我/o/q

我/o/q

我

我

我/o/q

我/clk

我/o/q

Vcc

SCLK

我/o/q

我/o/q

我

SDI

地

我

我

Vcc

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

SDO

我/o/q

我/o/q

我/o/q

我/o/q

我/o/q

我

SDI

SCLK

我/clk

我

我

我

我

我

模式

我

我

我

我

我

地

1

7

14

28

22

15

ispGAL

22V10

顶部 查看

SSOP

ispGAL22V10

顶部 查看

isp22v10_02