www.latticesemi.com

1

xpga_04

ispXPGA

家庭

march 2003 初步 数据 工作表

tm

© 2003 lattice 半导体 corp. 全部 lattice 商标, 已注册 商标, 专利, 和 免责声明 是 作为 已列出 在 www.latticesemi.com/legal. 全部 其他 品牌

或 产品 姓名 是 商标 或 已注册 商标 的 他们的 各自 持有人. 这 规格

fi

阳离子 和 信息 此处 是 主题 至 变更 无 通知.

■

非-挥发性, 入点

fi

nitely 侦察兵

fi

gurable

• 即时开启 - 权力 向上 入点 微秒 通过

片上 e?

2

CMOS

®

基于 记忆

• 否 外部 con

fi

配置 记忆

• 优秀 设计 安全, 否 有点 溪流 至 截距

• 侦察兵

fi

古雷 sram 基于 逻辑 入点 毫秒

■

高 逻辑 密度 用于 系统级

集成

• 139k 至 1.25m 系统 盖茨

• 160 至 496 我/o

• 1.8v, 2.5v, 和 3.3v v

抄送

操作

• 向上 至 414kb sysmem™ 嵌入式 记忆

■

高 业绩 可编程 功能

单位 (pfu)

•F我们的 lut-4 按 pfu 支架 宽 和 窄

功能

• 双

fl

ip-

fl

ops 按 lut-4 用于 广泛的 流水线

• 专用 逻辑 用于 加法器, 乘法器, 多路复用-

ers, 和 计数器

■

可变长度 互连 路由

technology

• 最佳 速度, 电源, 和

fl

exibility 用于 逻辑

互连

■

灵活 记忆 资源

• 多个 sysmem 嵌入式 ram 块

– 单独 港口, 双 港口, 和 先进先出 操作

• 64-有点 分布式 记忆 入点 每个 pfu

– 单独 港口, 双 港口, 先进先出, 和 轮班

注册 操作

■

八 sysclock™ 相位 已锁定 循环

(plls) 用于 时钟 管理

•True pll 技术

• 10mhz 至 320mhz 操作

• 时钟 乘法 和 事业部

• 相位 调整

• 轮班 时钟 入点 250ps 步骤

■

sysio™ 用于 高 系统 业绩

• 高 速度 记忆 支持 通过 sstl 和

HSTL

• 高级 公共汽车 支持 通过 pci, gtl+,

lvds, blvds, 和 lvpecl

• 标准 逻辑 支持 通过 lvttl,

lvcmos 3.3, 2.5, 和 1.8

• 可编程 驱动器 强度 用于 系列 终止

• 可编程 总线 维护保养

■

syshsi™ 能力 用于 超 快 串行

通信

• 向上 至 850mbps 业绩

• 向上 至 20 频道 按 设备

• 已建成 入点 时钟 数据 回收 (cdr) 和

序列化 和 反序列化 (serdes)

■

灵活 编程, 侦察兵

fi

配置,

和 测试

• ieee 1532 和 1149.1 符合

• 微处理器 con

fi

配置 接口

• 程序 e?

2

cmos 同时 操作 从 sram

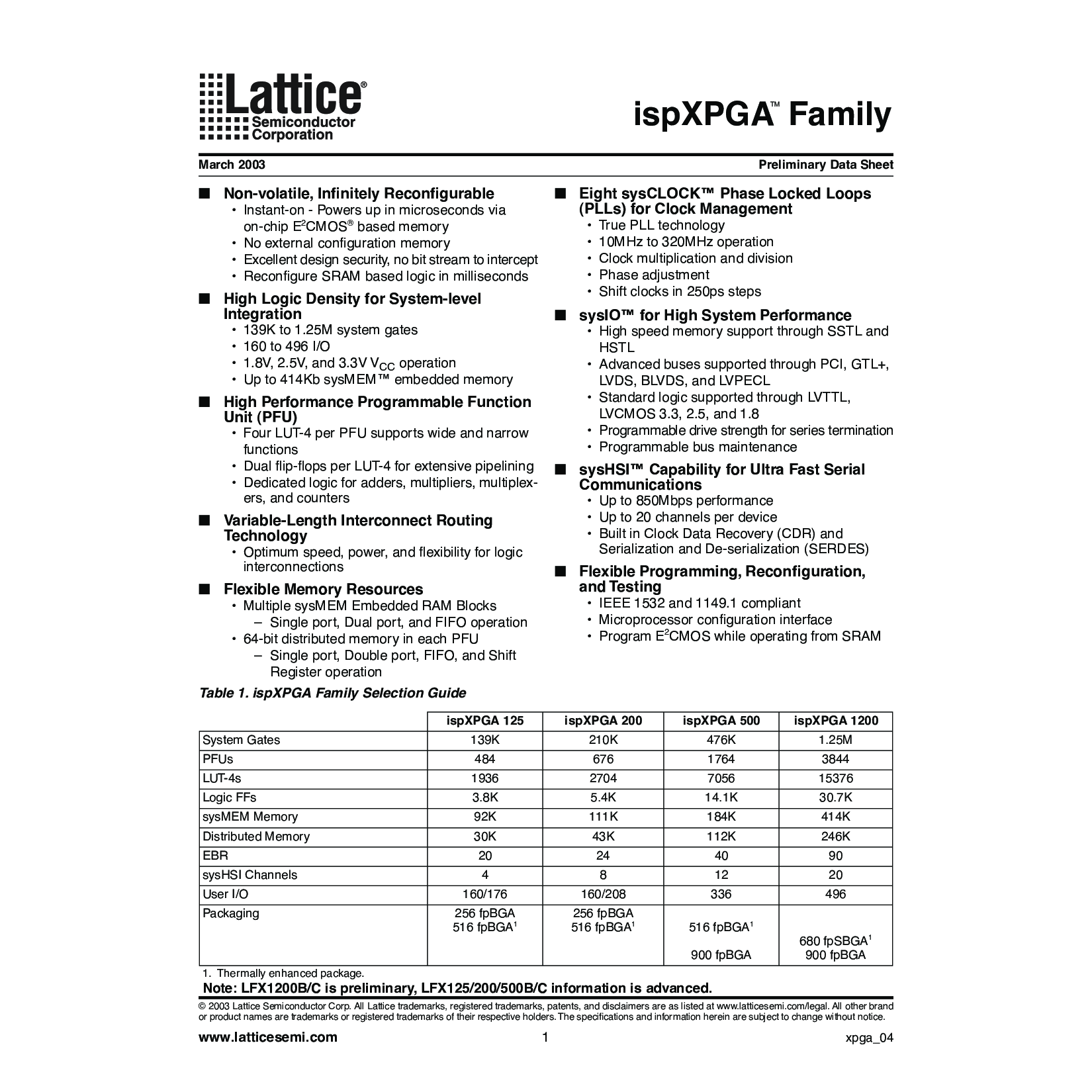

助教b乐 1. ispxpga 家庭 选择 指南

ispxpga 125 ispxpga 200 ispxpga 500 ispxpga 1200

系统 盖茨 139K 210K 476K 1.25m

PFUs 484 676 1764 3844

lut-4s 1936 2704 7056 15376

逻辑 ffs 3.8k 5.4k 14.1k 30.7k

sysmem 记忆 92K 111K 184K 414K

分布式 记忆 30K 43K 112K 246K

EBR 20 24 40 90

syshsi 频道 4 8 12 20

用户 我/o 160/176 160/208 336 496

packaging 256 fpbga

516 fpbga

1

256 fpbga

516 fpbga

1

516 fpbga

1

900 fpbga

680 fpsbga

1

900 fpbga

1. 热 增强型 包装.

备注: lfx1200b/c 是 初步, lfx125/200/500b/c 信息 是 advanced.