5-1

事实 数据

双 DĆType 正

EdgeĆTriggered FlipĆFlop

这 mc74ac74/74act74 是 一个 双 d-类型 触发器 与 异步 清除

和 设置 输入 和 互补 (q,q

) 产出. 信息 在 这 输入 是

已转移 至 这 产出 开启 这 正 边缘 的 这 时钟 脉冲. 时钟 触发

发生 在 一个 电压 水平 的 这 时钟 脉冲 和 是 不 直接 相关 至 这 过渡

时间 的 这 积极向上 脉冲. 之后 这 时钟 脉冲 输入 阈值 电压 有

被 通过, 这 数据 输入 是 已锁定 出点 和 信息 目前 将 不 是

已转移 至 这 产出 直到 这 下一个 上升 边缘 的 这 时钟 脉冲 输入.

异步 输入:

低 输入 至 s

d

(设置) 集 q 至 高 水平

低 输入 至 c

d

(清除) 集 q 至 低 水平

清除 和 设置 是 独立 的 时钟

同时 低 开启 c

d

和 s

d

使 两者都有 q 和 q

高

•

产出 来源/水槽 24 ma

• ′

act74 有 ttl 兼容 输入

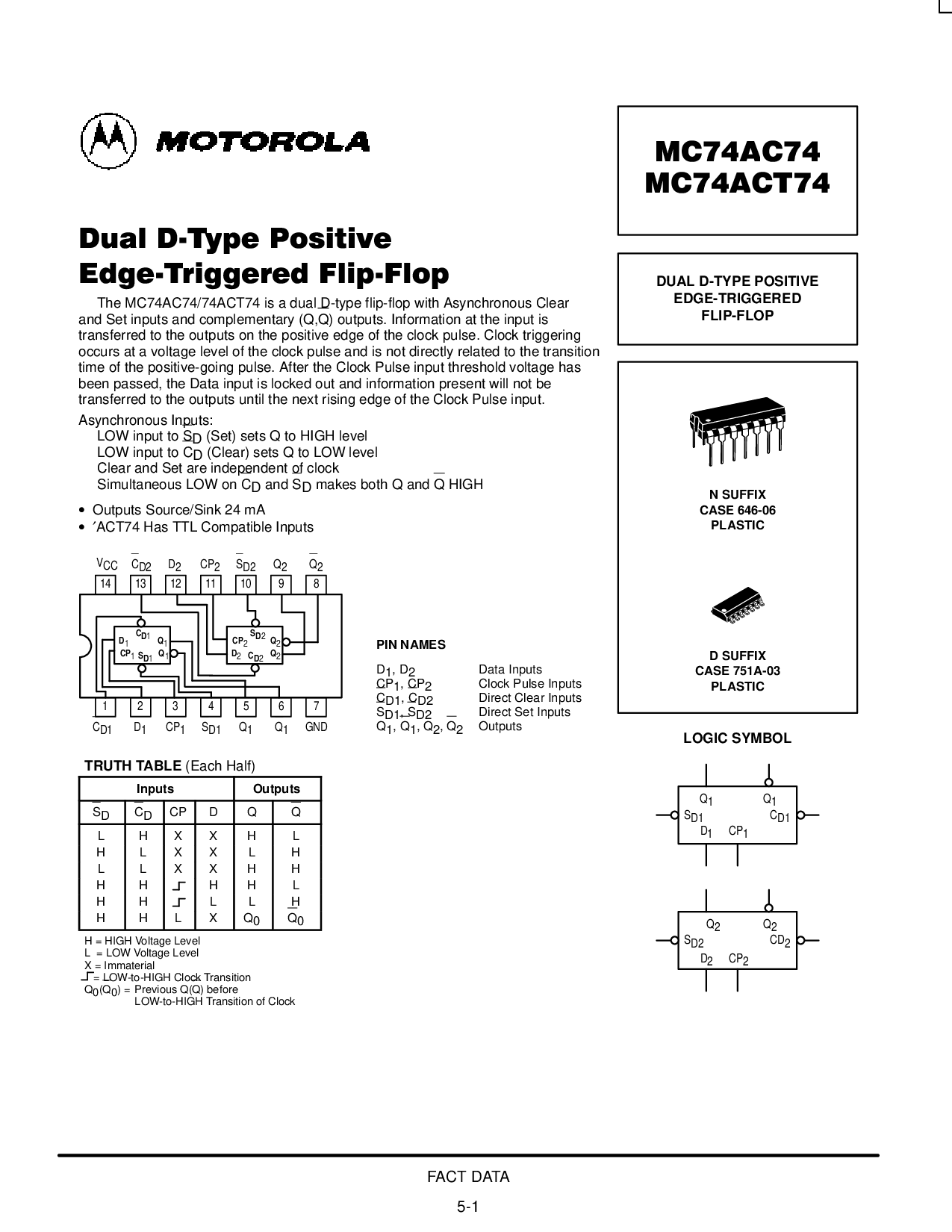

cp

1

c

d

2

cp

2

1314 12 11 10 9 8

21 3 4 5 6 7

v

抄送

c

D1

d

1

cp

1

s

D1

q

1

q

1

c

D2

d

2

cp

2

s

D2

q

2

q

2

c

d

1

s

d

1

q

1

d

1

s

d

2

q

2

q

2

d

2

地

q

1

管脚 姓名

d

1

, d

2

数据 输入

cp

1

, cp

2

时钟 脉冲 输入

c

D1

, c

D2

直接 清除 输入

s

D1

, s

D2

直接 设置 输入

q

1

, q

1

, q

2

, q

2

产出

真相 表

(每个 一半)

输入 产出

s

d

c

d

cp d q q

l h x x h l

h l x x l h

l l x x h h

h h h h l

h h l l h

h h l x q

0

q

0

h = 高 电压 水平

l = 低 电压 水平

x = 不重要

= 从低到高 时钟 过渡

q

0

(q

0

) = 上一个 q(q

) 之前

从低到高 过渡 的 时钟

MC74AC74

MC74ACT74

双 d-类型 正

边沿触发

触发器

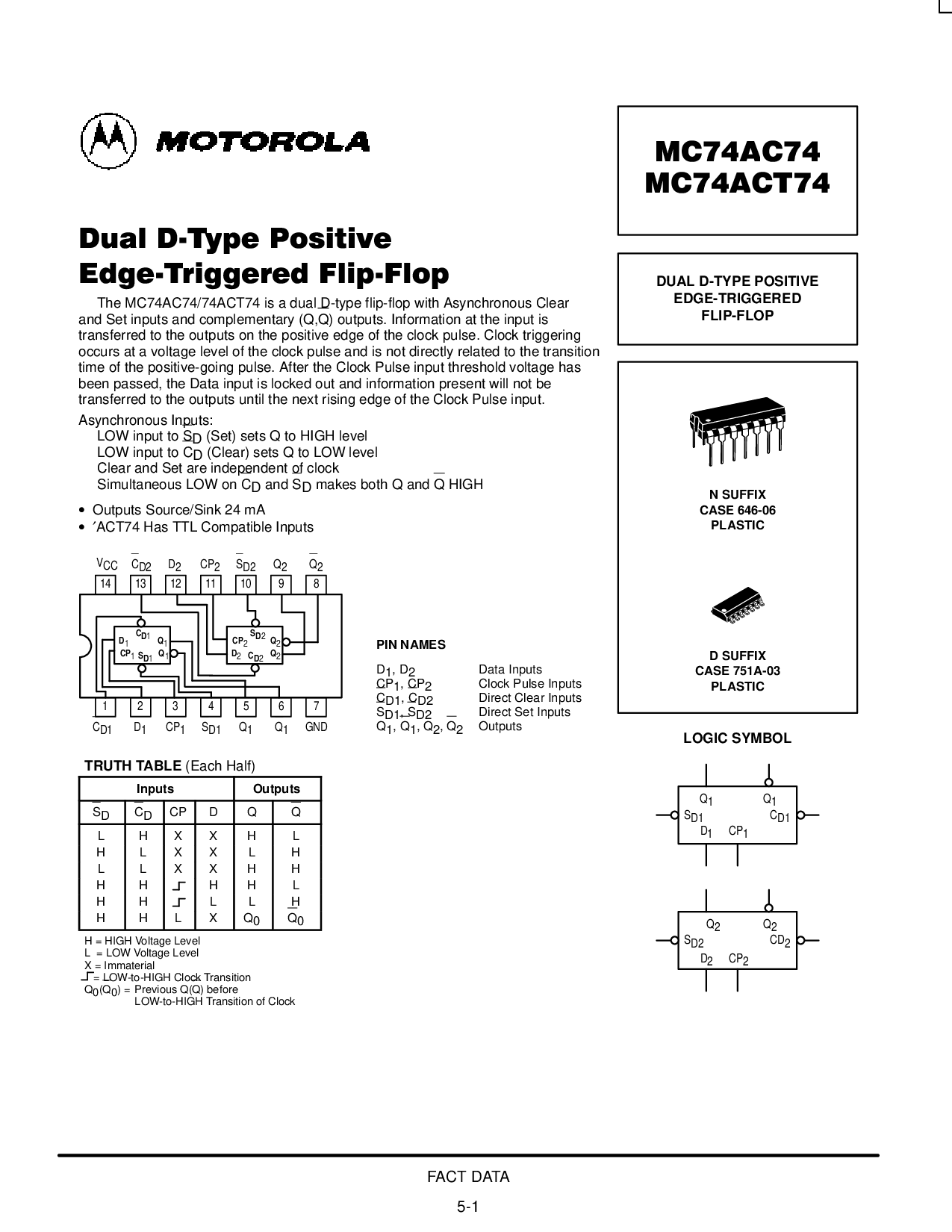

n 后缀

案例 646-06

塑料

d 后缀

案例 751a-03

塑料

逻辑 符号

s

D1

q

1

cp

1

q

1

c

D1

s

D2

q

2

d

2

cp

2

q

2

光盘

2

d

1