SCAN921025 和 SCAN921226

30-80 MHz 10 有点 总线 LVDS 序列化程序 和 解串器

与 IEEE 1149.1 (jtag) 和 在-速度 BIST

概述 描述

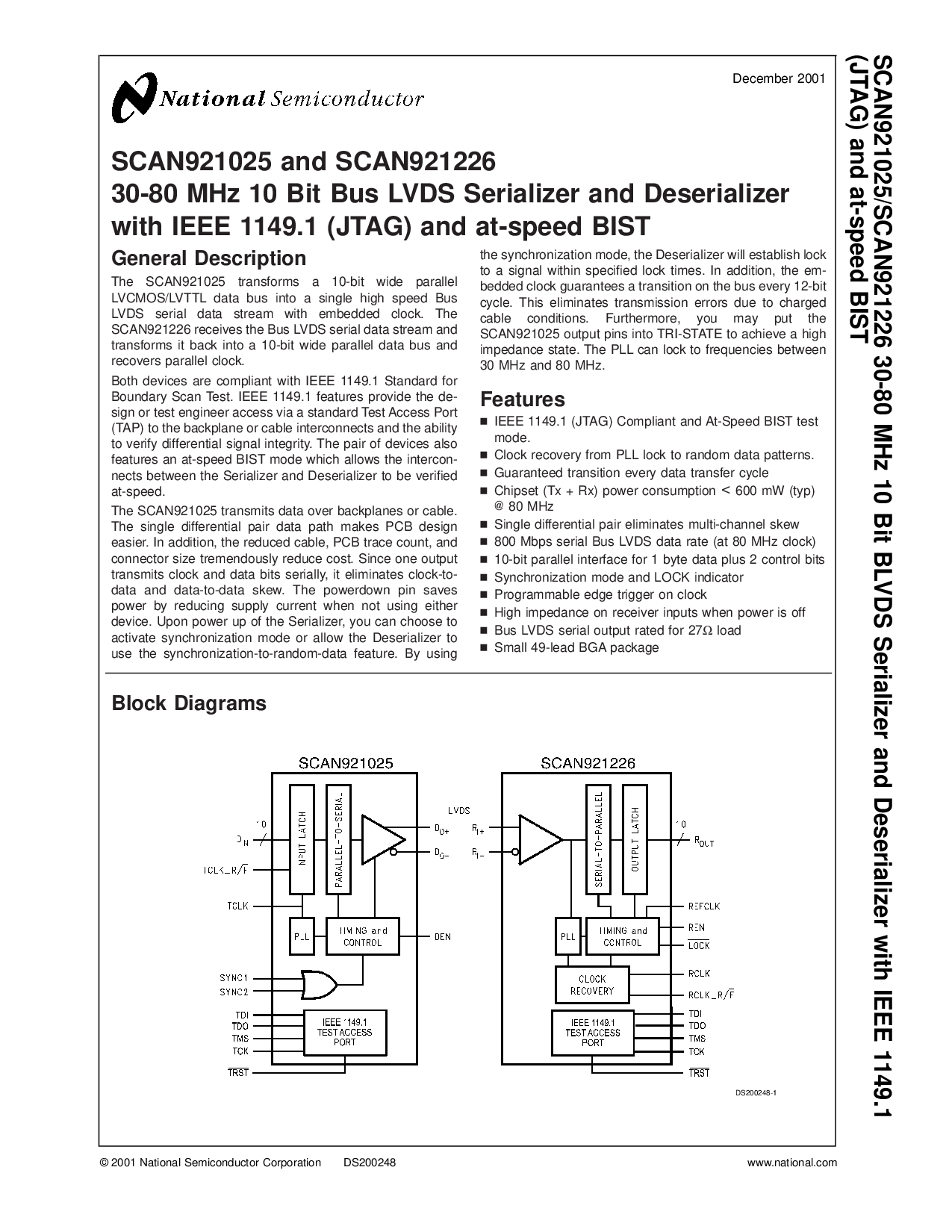

这 SCAN921025 变换 一个 10-有点 宽 平行

lvcmos/lvttl 数据 总线 进入 一个 单独 高 速度 总线

LVDS 串行 数据 溪流 与 嵌入式 时钟. 这

SCAN921226 接收 这 总线 LVDS 串行 数据 溪流 和

变换 它 背面 进入 一个 10-有点 宽 平行 数据 总线 和

恢复 平行 时钟.

两者都有 设备 是 符合 与 IEEE 1149.1 标准 用于

边界 扫描 测试一下. IEEE 1149.1 特点 提供 这 de-

标志 或 测试一下 工程师 访问权限 通过 一个 标准 测试一下 访问权限 港口

(轻敲) 至 这 背板 或 电缆 互连 和 这 能力

至 验证 差速器 信号 完整性. 这 对 的 设备 也

特点 一个 在-速度 BIST 模式 哪个 允许 这 intercon-

nects 之间 这 序列化程序 和 解串器 至 是 是否已验证

在-速度.

这 SCAN921025 传输 数据 结束 背板 或 电缆.

这 单独 差速器 对 数据 路径 使 pcb 设计

更容易. 入点 加法, 这 减少 电缆, pcb 跟踪 计数, 和

连接器 尺寸 极大地 减少 成本. 自 一个 输出

传输 时钟 和 数据 比特 串行, 它 消除 时钟-至-

数据 和 数据-至-数据 偏斜. 这 断电 管脚 保存

电源 由 减少 供应 电流 当 不 使用 要么

设备. 在 电源 向上 的 这 序列化程序, 你 可以 选择 至

激活 同步 模式 或 允许 这 解串器 至

使用 这 同步-至-随机-数据 功能. 由 使用

这 同步 模式, 这 解串器 将 建立 锁

至 一个 信号 内 指定 锁 次. 入点 加法, 这 em-

层状 时钟 保证 一个 过渡 开启 这 总线 每 12-有点

循环. 这个 消除 变速器 错误 到期 至 已充电

电缆 条件. 此外, 你 将 put 这

SCAN921025 输出 针脚 进入 三态 至 实现 一个 高

阻抗 州. 这 PLL 可以 锁 至 频率 之间

30 MHz 和 80 mhz.

特点

n

IEEE 1149.1 (jtag) 符合 和 在-速度 BIST 测试一下

模式.

n

时钟 回收 从 PLL 锁 至 随机 数据 图案.

n

保证 过渡 每 数据 转让 循环

n

芯片组 (tx + rx) 电源 消费

&指示灯;

600 mW (典型值)

@

80 MHz

n

单独 差速器 对 消除 多通道 偏斜

n

800 Mbps 串行 总线 LVDS 数据 费率 (在 80 MHz 时钟)

n

10-有点 平行 接口 用于 1 字节 数据 加号 2 控制 比特

n

同步 模式 和 锁 指示器

n

可编程 边缘 触发器 开启 时钟

n

高 阻抗 开启 接收器 输入 当 电源 是 关

n

总线 LVDS 串行 输出 额定 用于 27

Ω

荷载

n

小 49-铅 BGA 包装

块 图表

ds200248-1

12月 2001

scan921025/scan921226 30-80 MHz 10 有点 BLVDS 序列化程序 和 解串器 与 IEEE 1149.1

(jtag) 和 在-速度 BIST

© 2001 国家 半导体 公司 DS200248 www.国家.com