W24L011A

128K

×

8 高 速度 cmos s塔蒂克 ram

出版物 释放 日期:april 26, 2002

-1-修订 a3

概述 描述

这w24l011a 是 一个 高 速度, 低 电源 cmos 静态 ram 有组织的 作为 131072 x 8 比特 那

操作 开启 一个 单独 3.3-电压 电源 供应. 这个 设备 是 已制造 使用winbond's 高

业绩 cmos 技术.

特点

•

高 速度 交流电cess 时间: 10/12/15 ns

•

单独 +3.3v 电源 供应

•

中心 电源/接地 管脚 配置

•

完全 静态 操作

•

全部 输入 和 产出 直接 ttl 兼容

•

三个-州 产出

•

可用 软件包: 32-管脚 300 密耳 soj, 小

TSOP-我(8 x 13.4 mm),TSOP-我(8 x 20 mm)

和 400 密耳 soj

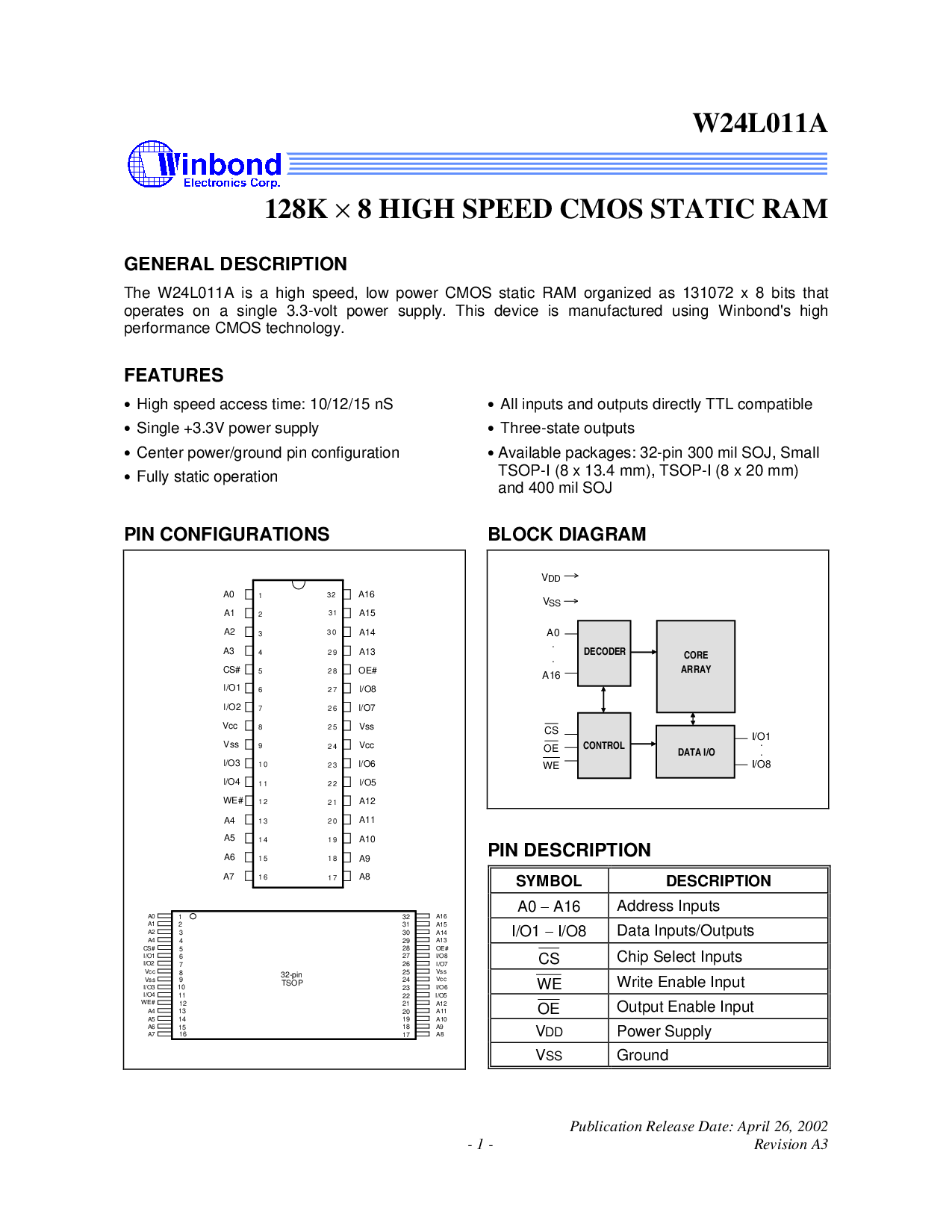

管脚 配置

1

2

3

4

5

2 4

2 5

2 6

2 7

2 8

6

7

8

9

2 0

2 1

2 2

2 3

1 0

1 1

1 2

1 3

1 6

1 7

1 8

1 9

1 4

1 5

3 2

3 1

3 0

2 9

1

2

3

4

5

6

7

8

9

11

12

14

15

16

32-管脚

TSOP

32

31

30

29

27

26

25

24

23

22

21

20

19

18

17

10

13

28

A0

A1

A2

A3

CS#

我/o1

我/o2

Vcc

vss

我/o3

我/o4

WE#

A4

A5

A6

A7 A8

A9

A10

A11

A12

我/o5

我/o6

Vcc

vss

我/o7

我/o8

OE#

A13

A14

A15

A16

A8

A9

A10

A11

A12

我/o5

我/o6

Vcc

vss

我/o7

我/o8

OE#

A13

A14

A15

A16

A0

A1

A2

A4

CS#

我/o1

我/o2

Vcc

vss

我/o3

我/o4

WE#

A4

A5

A6

A7

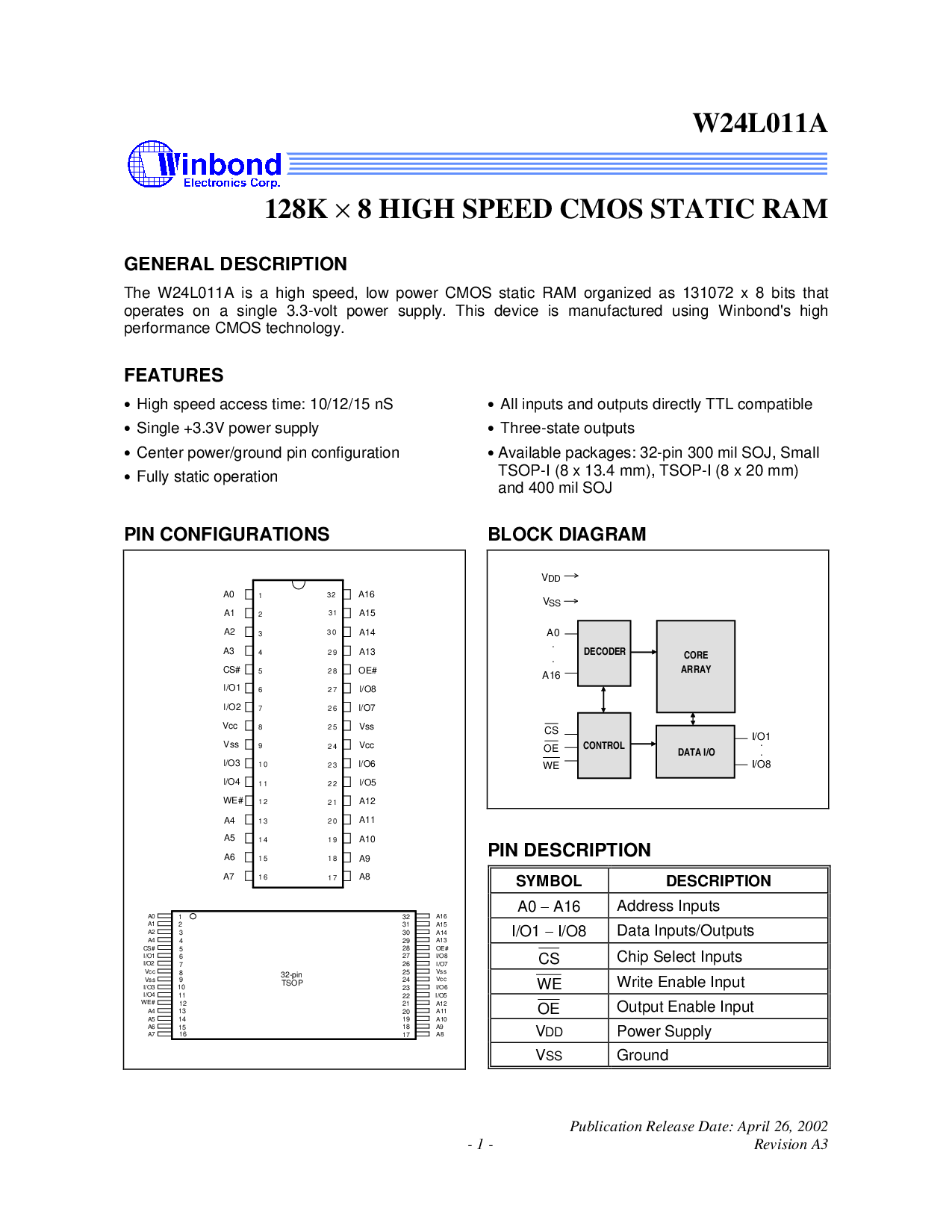

块 图表

A0

.

cs

A16

我们

我/o1

我/o8

oe

v

v

.

.

数据 我/o

阵列

解码器

核心

.

控制

dd

ss

管脚 描述

符号 描述

A0

−

A16

地址 输入

我/o1

−

我/o8

数据 输入/产出

cs

芯片 选择 输入

我们

写 启用 输入

oe

输出 启用 输入

vdd

电源 供应

vss

接地