频率 控制器 与 系统 回收

用于 英特尔

综合 核心 逻辑

W305B

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07262 rev. *b 修订 九月 1, 2004

特点

• 单独 芯片 ftg 解决方案 用于 英特尔 solano/810e/810

• 可编程 时钟 输出 频率 与 较少 比

1 mhz 增量

• 综合 故障安全 watchdog 计时器 用于 系统

回收

• 自动 开关 至 hw 已选择 或 软件

编程 时钟 频率 当 看门狗 计时器

超时

• 有能力 的 生成 系统 重置 之后 一个 看门狗

计时器 超时 发生 或 一个变更 入点 输出 频率

通过 smbus 接口

• 支持 smbus 字节 阅读/写 和 块 阅读/写

运营 至 简化 系统 bios 发展

• 供应商 id 和 修订 id 支持

• 可编程 驱动器 强度 用于 sdram 和 pci

输出 时钟

• 可编程 输出 偏斜 之间 cpu, agp, pci

和 sdram

• 最大化 emi 抑制 使用 柏树’s 传播

光谱 技术

• 低 抖动 和 紧紧地受控 时钟 偏斜

• 两个 副本 的 cpu 时钟

• 十三 副本 的 sdram 时钟

• 八 副本 的 pci 时钟

• 一个 复制 的 同步 apic 时钟

• 三个 副本 的 66-mhz 产出

• 三个 副本 的 48-mhz 产出

• 一个 复制 的 双 强度 14.31818-mhz 参考

时钟

• 一个 重置 输出用于 系统 回收

• smbus 接口 用于 turning 关 未使用 时钟

钥匙 规格

cpu, sdram 产出 循环到循环 抖动: ............. 250 ps

apic, 48-mhz, 3v66, pci 产出

循环到循环 抖动:................................................... 500 ps

cpu, 3v66 输出 偏斜: ........................................... 175 ps

sdram, apic, 48-mhz 输出 偏斜: ....................... 250 ps

pci 输出 偏斜: ....................................................... 500 ps

cpu 至 sdram 偏斜 (@ 133 mhz) ....................... ± 0.5 ns

cpu 至 sdram 偏斜 (@ 100 mhz) ................. 4.5 至 5.5 ns

cpu 至 3v66 偏斜 (@ 66 mhz)........................ 7.0 至 8.0 ns

3v66 至 pci 偏斜 (3v66 铅) .......................... 1.5 至 3.5 ns

pci 至 apic 偏斜..................................................... ± 0.5 ns

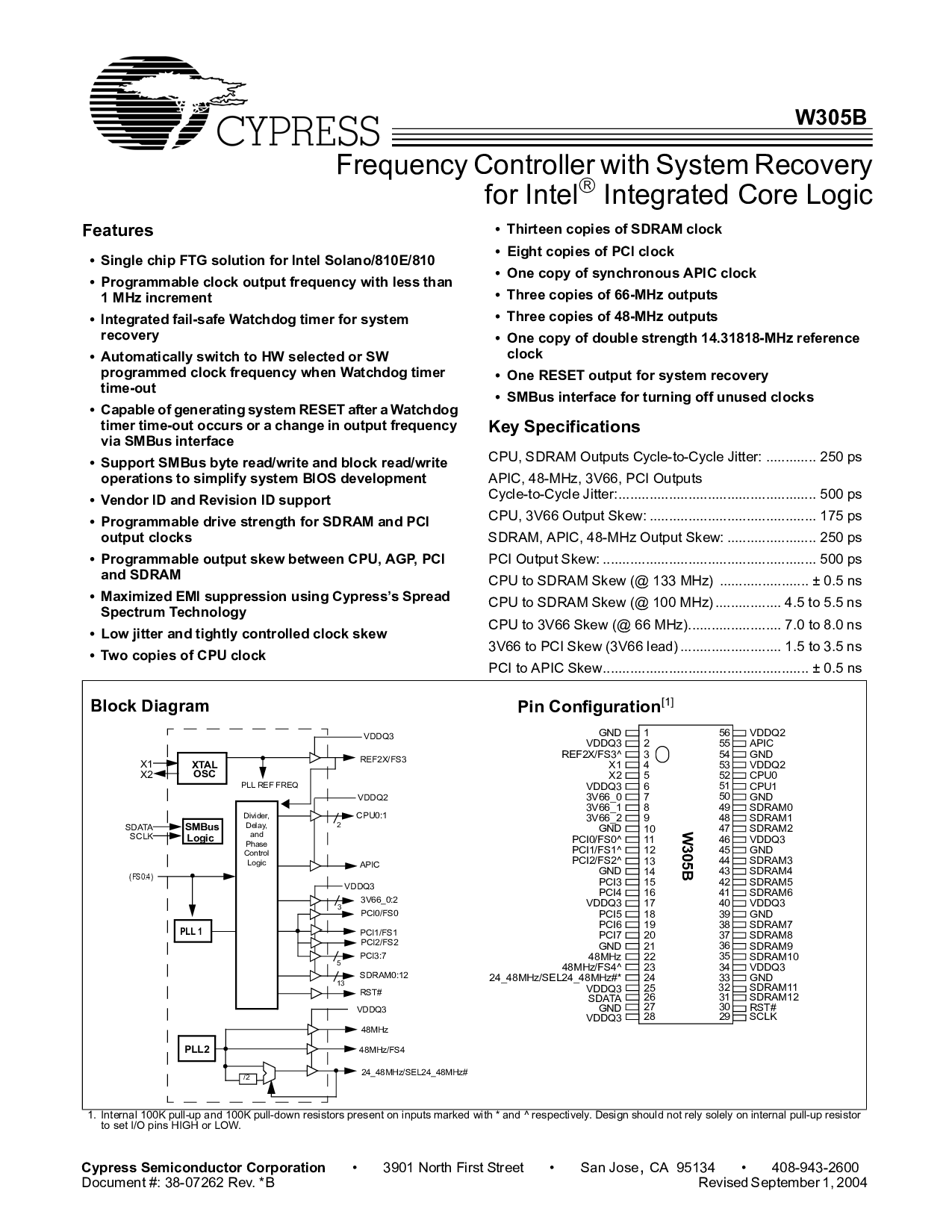

1. 内部 100k 上拉 和 100k 下拉 电阻 目前 开启 我输入 已标记 与 * 和 ^ 分别. 设计 应该 不 依靠仅 开启 内部 上拉 电阻

至 设置 我/o 针脚 高 或 低.

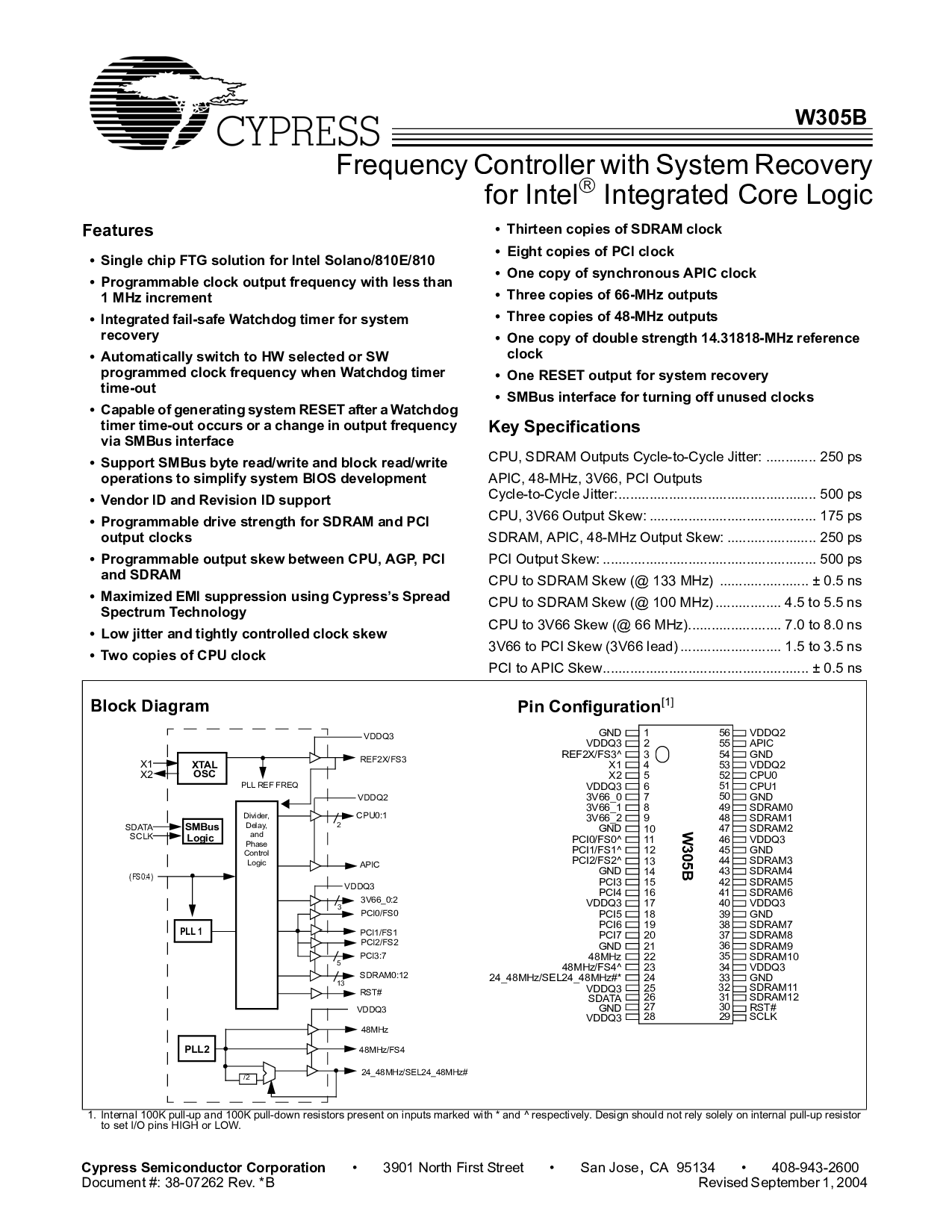

块 图表

管脚 配置

[1]

VDDQ3

VDDQ2

pci1/fs1

XTAL

pll 参考 频率

pll 1

X2

X1

ref2x/fs3

pci3:7

48mhz/fs4

24_48mhz/sel24_48mhz#

PLL2

osc

VDDQ3

SMBus

SDATA

逻辑

SCLK

3v66_0:2

cpu0:1

APIC

分隔器,

延迟,

和

相位

控制

逻辑

3

VDDQ3

2

sdram0:12

13

RST#

pci0/fs0

pci2/fs2

/2

(fs0:4)

5

48MHz

地

VDDQ3

ref2x/fs3^

X1

X2

VDDQ3

3v66_0

3v66_1

3v66_2

地

pci0/fs0^

pci1/fs1^

pci2/fs2^

地

PCI3

PCI4

VDDQ3

PCI5

PCI6

PCI7

地

48MHz

48mhz/fs4^

24_48mhz/sel24_48mhz#*

W305B

VDDQ2

APIC

地

VDDQ2

CPU0

CPU1

地

SDRAM0

SDRAM1

SDRAM2

VDDQ3

地

SDRAM3

SDRAM4

SDRAM5

SDRAM6

VDDQ3

地

SDRAM7

SDRAM8

SDRAM9

SDRAM10

VDDQ3

地

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

32

31

30

29

VDDQ3

SDATA

地

VDDQ3

SDRAM11

SDRAM12

RST#

SCLK