1

描述

这 cat5419 是 两个 数字 可编程

电位计 (dpp™) 综合 与 控制 逻辑

和 16 字节数 的 nvram 记忆.

一个 分开 6-有点 控制 注册 (wcr) 独立

控件 这 雨刮器 轻敲 位置 用于 每个 dpp. 关联的

与 每个 雨刮器 控制 注册 是 四 6-有点 非-

挥发性 记忆 数据 寄存器 (博士) 已使用 用于 存储 向上

至 四 雨刮器 设置. 写作 至 这 雨刮器 控制 注册

或 任何 的 这 非挥发性 数据 寄存器 是 通过 一个 2-电线

串行 总线 (我

2

c-喜欢). 开启 电源-向上, 这 内容 的 这

CAT5419

双 数字 可编程 电位计 (dpp™) 与

64 水龙头 和 2-电线 接口

特点

■

两个 线性-taper 数字 电位计

■

64 电阻 水龙头 按 电位计

■

端到端 电阻 2.5k

Ω

, 10k

Ω

, 50k

Ω

或 100k

Ω

■

电位计 控制 和 记忆 访问权限 通过

2-电线 接口 (我

2

c 喜欢)

■

低 雨刮器 电阻, 通常 80

ΩΩ

ΩΩ

Ω

■

四 非挥发性 雨刮器 设置 用于 每个

电位计

■

召回 的 雨刮器 设置 在 电源 向上

■

2.5 至 6.0 电压 操作

■

备用 电流 较少 比 1

µ

一个

■

1,000,000 非挥发性 写 循环次数

■

100 年份 非挥发性 记忆 数据 保留

■

24-铅 soic, 24-铅 tssop 和 bga

■

写 保护 用于 数据 注册

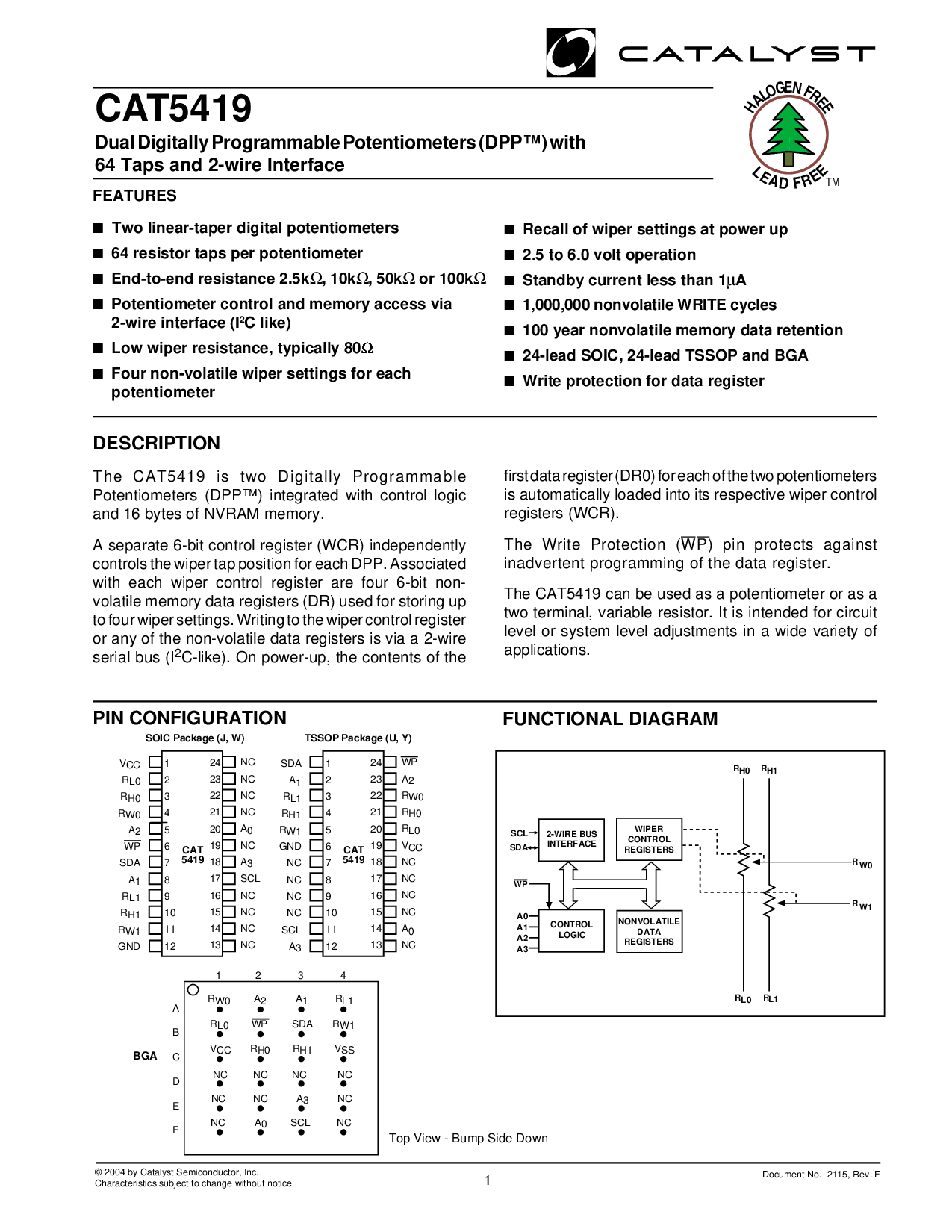

管脚 配置

功能 图表

© 2004 由 catalyst 半导体, 公司

特性 主题 至 变更 无 通知

文件 否. 2115, rev. f

第一 数据 注册 (dr0) 用于 每个 的 这 两个 电位计

是 自动 已加载 进入 其 各自 雨刮器 控制

寄存器 (wcr).

这 写 保护 (

WP

) 管脚 保护 反对

无意 编程 的 这 数据 注册.

这 cat5419 可以 是 已使用 作为 一个 电位计 或 作为 一个

两个 终端, 变量 电阻. 它 是 预期 用于 电路

水平 或 系统 水平 调整 入点 一个 宽 品种 的

应用程序.

BGA

顶部 查看 - 颠簸 侧面 向下

W1

W0

H0

H1

右

右

L0

L1

右

右

雨刮器

控制

寄存器

非挥发性

数据

寄存器

2-电线 总线

接口

控制

逻辑

scl

SDA

WP

A0

A1

A2

A3

右

右

h

一个

l

o

g

e?

n

f

右

e?

e?

tm

l

e?

一个

d

f

右

e?

e?

1 2 3 4

一个

B

c

d

e?

f

右

W0

一个

2

一个

1

右

L1

右

L0

WP

SDA 右

W1

v

抄送

右

H0

右

H1

v

ss

nc nc nc nc

nc nc 一个

3

nc

nc 一个

0

scl nc

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

CAT

5419

v

抄送

右

L0

右

H0

右

W0

一个

2

WP

SDA

一个

1

右

L1

右

H1

右

W1

地

nc

nc

nc

nc

一个

0

nc

一个

3

scl

nc

nc

nc

nc

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

CAT

5419

SDA

一个

1

右

L1

右

H1

右

W1

地

nc

nc

nc

nc

scl

一个

3

WP

一个

2

右

W0

右

H0

右

L0

v

抄送

nc

nc

nc

nc

一个

0

nc

soic 包装 (j, w) tssop 包装 (u, y)