spi 串行 e?

2

舞会 与 块 锁

tm

保护

128K

16k x 8 有点

xicor 公司 1994, 1995, 1996 专利 待定 特性 主题 至 变更 无 通知

3091-2.9 5/14/97 t2/c0/d2 sh

1

X25128

一个

应用

n

OTE

availAB l e?

AN61

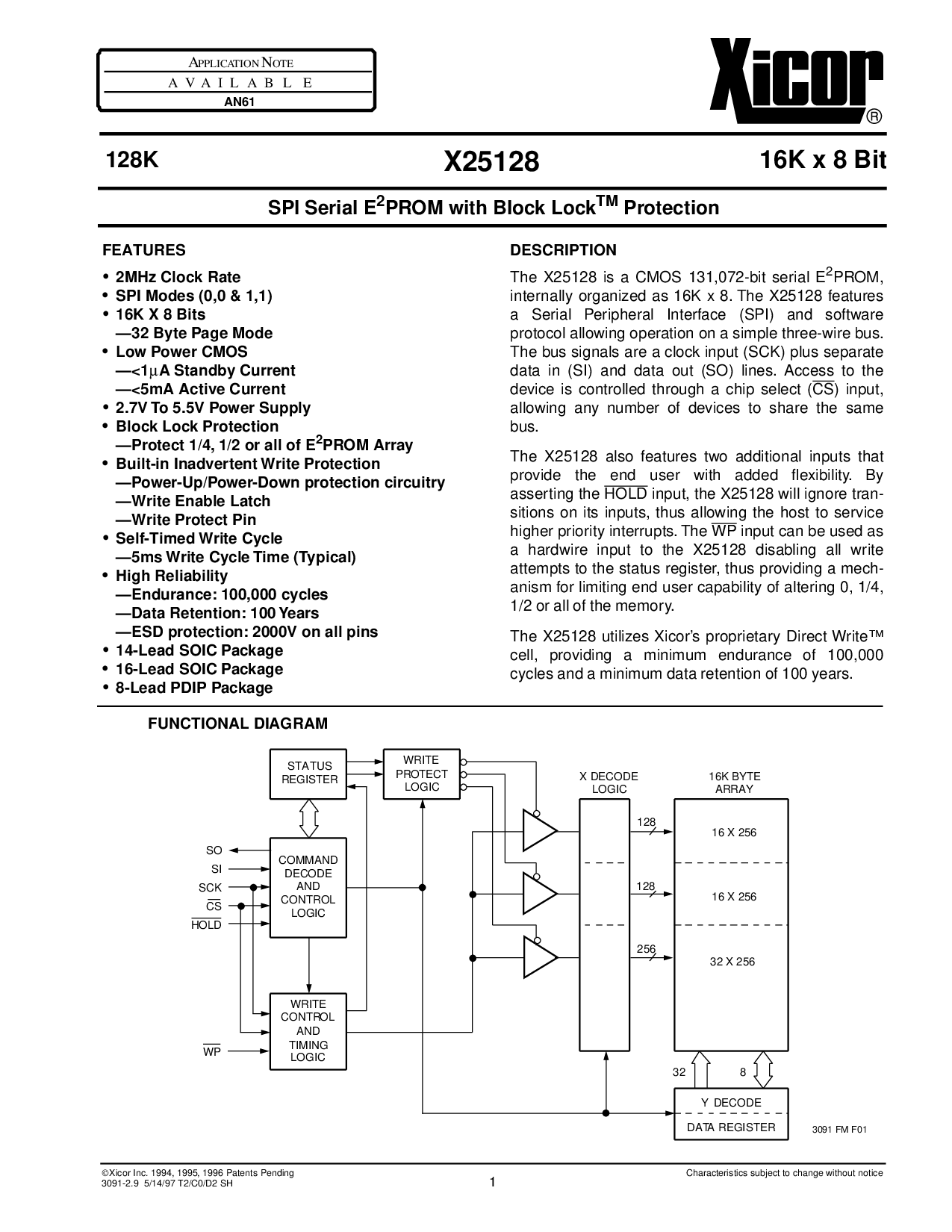

功能 图表

命令

解码

和

控制

逻辑

写

控制

和

计时

逻辑

写

保护

逻辑

x 解码

逻辑

16k 字节

阵列

16 x 256

y 解码

数据 注册

所以

si

sck

cs

保持

WP

832

32 x 256

16 x 256

3091 调频 f01

128

128

256

状态

注册

特点

•

2mhz 时钟 费率

•

spi 模式 (0,0 &放大器; 1,1)

•

16k x 8 比特

—32 字节 第页 模式

•

低 电源 cmos

—&指示灯;1

µ

一个 备用 电流

—&指示灯;5ma 活动 电流

•

2.7v 至 5.5v 电源 供应

•

块 锁 保护

—protect 1/4, 1/2 或 全部 的 e?

2

舞会 阵列

•

内置 无意 写 保护

—power-向上/电源-向下 保护 电路

—write 启用 门闩

—write 保护 管脚

•

自定时 写循环

—5ms 写 循环 时间 (典型)

•

高 可靠性

—endurance: 100,000 循环次数

—data 保留: 100 年

—esd 保护: 2000v 开启 全部 针脚

•

14-铅 soic 包装

•

16-铅 soic 包装

•

8-铅 pdip 包装

描述

这 x25128 是 一个 cmos 131,072-有点 串行 e?

2

舞会,

内部 有组织的 作为 16k x 8. 这 x25128 特点

一个 串行 外围设备 接口 (spi) 和 软件

协议 允许 操作 开启 一个 简单 三线 总线.

这 总线 信号 是 一个 时钟 输入 (sck) 加号 分开

数据 入点 (si) 和 数据 出点 (所以) 线条. 访问权限 至 这

设备 是 受控 通过 一个 芯片 选择 (cs) 输入,

允许 任何 号码 的 设备 至 分享 这 相同

总线.

这 x25128 也 特点 两个 附加 输入 那

提供 这 结束 用户 与 已添加 fl. 由

断言 这 保持 输入, 这 x25128 将 忽略 tran-

位置 开启 其 输入, 因此 允许 这 主机 至 服务

较高 优先 中断. 这 wp 输入 可以 是 已使用 作为

一个 硬线 输入 至 这 x25128 正在禁用 全部 写

尝试次数 至 这 状态 注册, 因此 提供 一个 机械-

anism 用于 限制 结束 用户 能力 的 改变 0, 1/4,

1/2 或 全部 的 这 记忆.

这 x25128 利用 xicor’s 专有 直接 write™

细胞, 提供 一个 最小值 耐力 的 100,000

循环次数 和 一个 最小值 数据 保留 的 100 年.