TC51WKM516AXBN75

2002-08-22 1/11

•

访问权限 次:

访问权限 时间 75 ns

CE1

访问权限 时间 75 ns

oe

访问权限 时间 25 ns

第页 访问权限 时间 30 ns

•

包装:

p-tfbga48-0607-0.75az (重量: g 典型值.)

TENTATIVE

toshiba mos 数字 integrated 电路 硅 闸门 cmos

2,097,152-字 由 16-有点 cmos 伪 静态 ram

描述

这 tc51wkm516axbn 是 一个 33,554,432-有点 伪 静态 随机 访问权限 记忆(psram) 有组织的 作为

2,097,152 字词 由 16 比特. 使用 toshiba’s cmos 技术 和 高级 电路 技术, 它 提供 高

密度, 高 速度 和 低 电源. 这 设备 用途 双电源 供应品(2.6 至 3.3 v fo右 核心 和 1.7 至 2.2 v 用于

输出 缓冲区). 这 设备 也 特点 sram-like? w/右 计时 由此 这 设备 是 受控 由

CE1 , oe , 和

我们 开启 异步. 这 设备 有 这 第页 访问权限 operat离子. 第页 尺寸 是 8 字词. 这 设备 也 支架

深 掉电 模式, 实现 低功耗 备用.

特点

•

有组织的 作为 2,097,152 字词 由 16 比特

•

双 电源 供应品(2.6 至 3.3 v 用于 核心 和

1.7 至 2.2 v 用于 输出 缓冲区)

•

直接 ttl 兼容性 用于 全部 输入 和 产出

•

深 掉电 模式: 记忆 细胞 数据 无效

•

第页 操作 模式:

第页 阅读 操作 由 8 字词

•

逻辑 兼容 与 sram 右/w (

我们

) 管脚

•

备用 电流

备用 70

µ

一个

深 掉电 备用 5

µ

一个

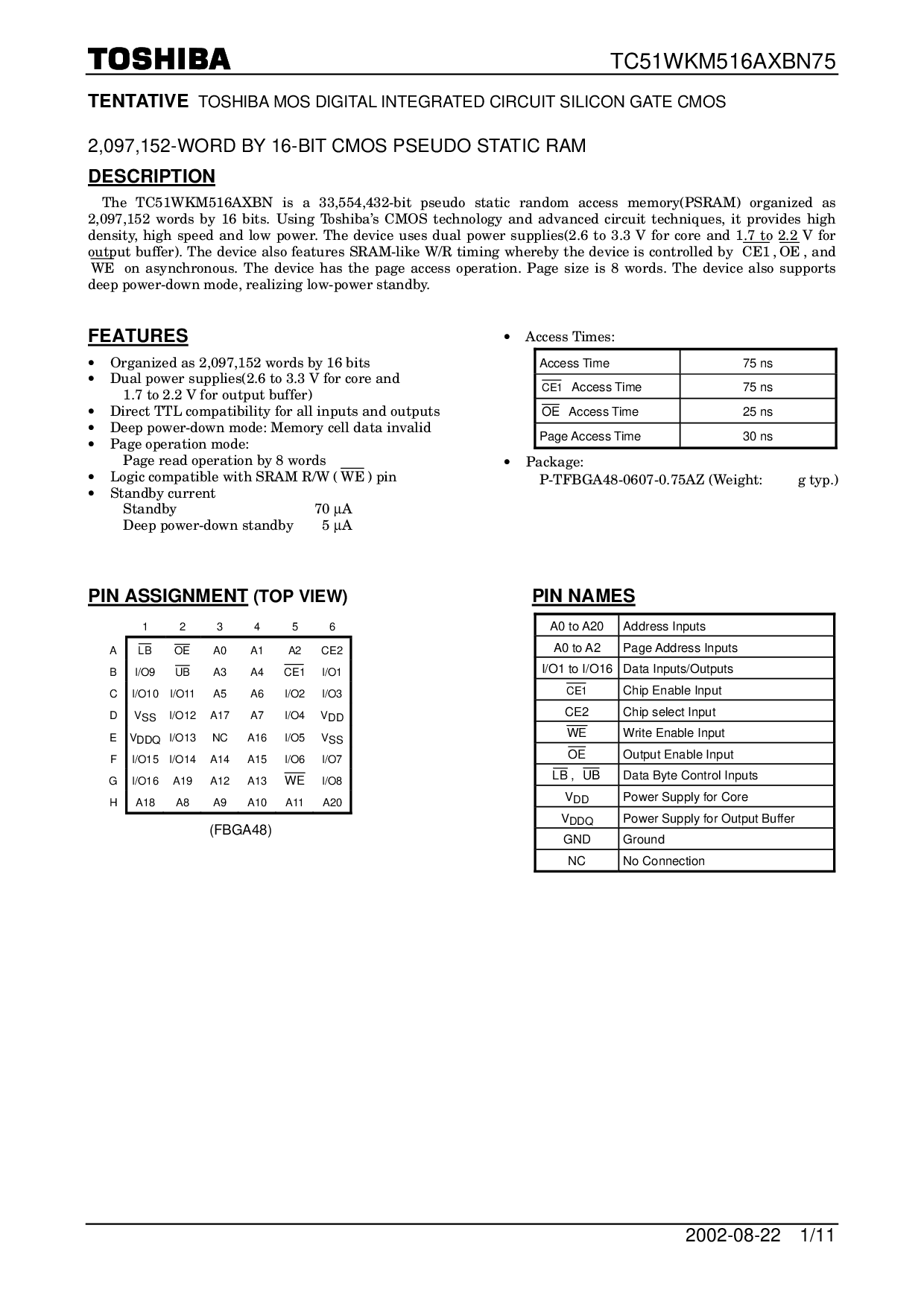

管脚 分配

(顶部 查看)

管脚 姓名

1 2 3 4 5 6

一个

磅

oe

a0 a1 a2 ce2

b 我/o9

ub

A3 A4

CE1 我/o1

c 我/o10 我/o11 A5 A6 我/o2 我/o3

d v

ss

我/o12A17 A7 我/o4 v

dd

e? v

DDQ

我/o13 nc A16我/o5 v

ss

f 我/o15 我/o14 A14 A15 我/o6 我/o7

g 我/o16 a19 A12 A13

我们

我/o8

h a18 A8 A9 a10 a11 a20

(fbga48)

a0 至 a20

地址 输入

a0 至 a2 第页 地址 输入

我/o1 至 我/o16 数据 输入/产出

CE1

芯片 启用 输入

CE2

芯片 选择 输入

我们 写 启用 输入

oe 输出 启用 输入

磅 ,

ub

数据 字节 控制 输入

v

dd

电源 供应 用于 核心

v

DDQ

电源 供应 用于 输出 缓冲区

地 接地

nc 否 连接