ds077-1 (v1.0) 十一月 15, 2001

www.xilinx.com

1

初步 产品 规格

1-800-255-7778

© 2001 xilinx, 公司 全部 权利 保留. 全部 xilinx 商标, 已注册 商标, patents, 和 免责声明 是 作为 已列出 一个t

http://www.xilinx.com/法律.htm

.

全部 其他 商标 和 已注册 商标 是 这 财产 的 他们的 各自 业主. 全部 规格 是 主题 至 change 无 通知.

导言

这 翼梁tan™-iie 1.8v 字段-可编程 闸门 阵列

家庭 给出 用户 高 业绩, abundant 逻辑

资源, 和 一个 富有 功能 设置, 全部 在 一个 例外情况 低

价格. 这 五个-会员 家庭 优惠 密度 测距 从

50,000 至 300,000 系统 盖茨, 作为 显示 入点助教 bl e? 1 . 系统-

透射电镜 业绩 是 支持 超越 200 mhz.

spartan-iie 设备 交付 更多 盖茨, 我/操作系统, 和 特点

按 dollar 比 其他 fpgas 由 组合 高级 专业版-

cess 技术 与 一个 streamlined 体系结构 基于 开启

这 经过验证 virtex™-e? 站台. 特点 包括 块 ram

(至 64k 比特), 分布式 ram (至 98,304 bits), 19 可选择

我/o 标准, 和 四 dlls (延迟-已锁定 循环). fast,

可预测 互连 手段 那 连续 设计 iter-

参数 继续 至 满足 计时 要求.

这 翼梁棕褐色-iie 家庭 是 一个 上级 备选方案 至

面具-编程 asics. 这 fpga 避免 这 初始 成本,

lengthy 发展 循环次数, 和 固有的 风险 的

常规 asics. 也, fpga 可编程性 许可证

设计 升级 入点 这 字段 与 否 硬件 更换

必要的 (不可能 与 asics).

特点

• 第二 世代 asic 更换 技术

- 密度 作为 高 作为 6,912 逻辑 细胞 与 向上 至

300,000 系统 盖茨

- streamlined 特点 基于 开启 virtex-e?

体系结构

- 无限 在系统内 可重新编程性

- 很 低 成本

• 系统 水平 特点

- selectram+™ hierarchical 记忆:

·

16 比特/lut 分布式 ram

·

可配置 4k-有点 真 双端口 块 ram

·

快 接口 至 外部 ram

- 完全 3.3v pci 符合 至 64 比特 在 66 mhz 和

cardbus 符合

- 低功耗 分段 路由 体系结构

- 已满 回读 能力 用于 验证/observability

- 专用 进位 逻辑 用于 高速 算术

- 高效 乘数 support

- 级联 链条 用于 宽输入 功能

- abundant 寄存器/锁扣 与 启用, 设置, 重置

- 四 专用 dlls 用于 高级 时钟 控制

- 四 主要

低偏斜

全球

时钟

分布

nets

- ieee 1149.1 兼容 边界 扫描 逻辑

•

多才多艺 我/o 和 包装

- 低 成本 软件包 可用 入点 全部 密度

- 家庭 占地面积 兼容性 入点 普通 软件包

- 19 高性能 接口 标准, 包括

lvds一个nd lvpe?cl

- 向上 至 120 差速器 我/o 对 那 可以 是 输入,

输出, 或 双向

- 零 保持 时间 简化了 系统 计时

•

完全 suppor泰德 由 强大的 xilinx ise 发展

系统

- 完全 自动 映射, 放置位置, 和 路由

- 综合 与 设计 进入 和 验证 工具

0

spartan-iie 1.8v fpga 家庭:

导言 和 订购

信息

ds077-1 (v1.0) 十一月 15, 2001

00

初步 产品 规格

右

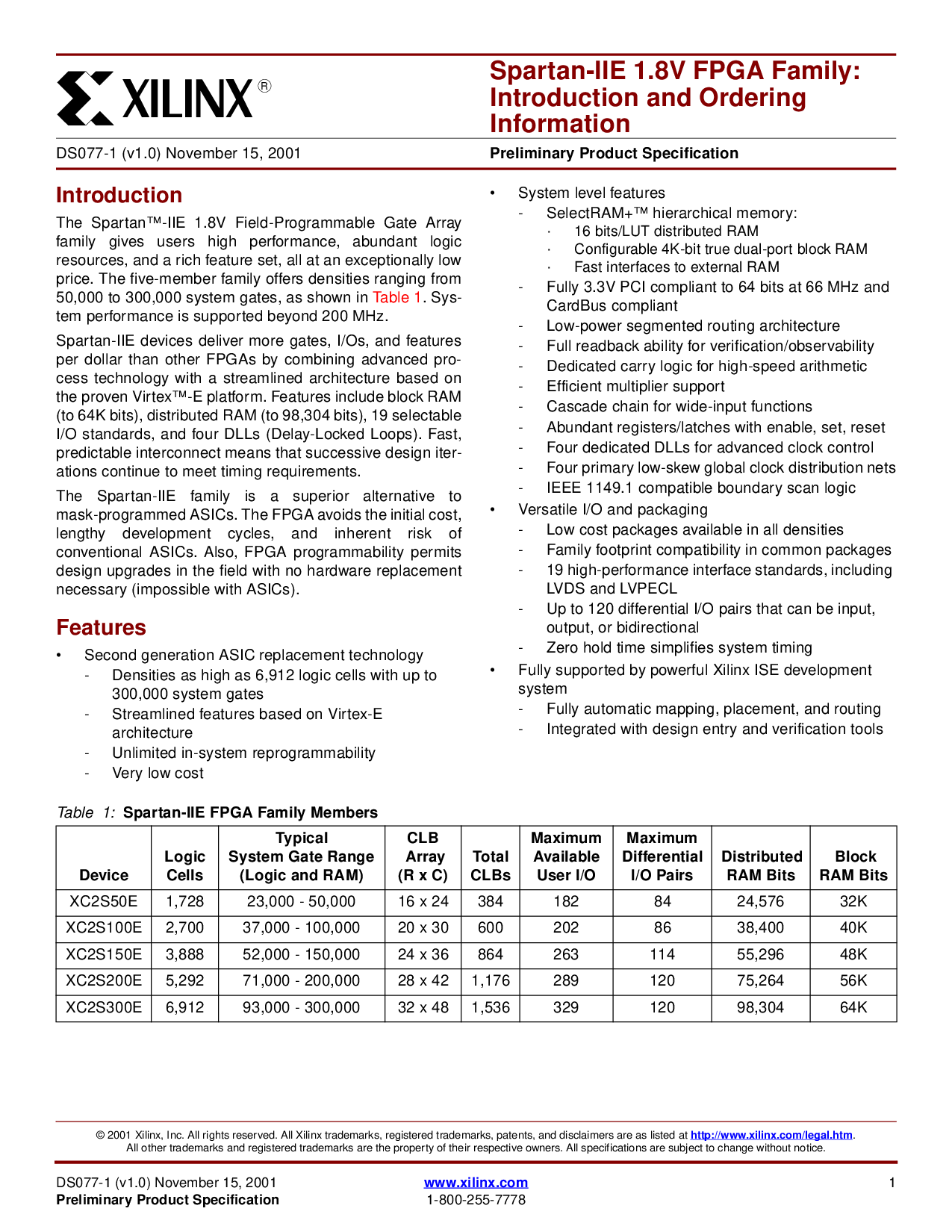

表 1:

spartan-iie fpga 家庭 成员

设备

逻辑

细胞

Typ集成电路一个l

系统 闸门 范围

(逻辑 和 ram)

CLB

阵列

(右 x c)

至t一个l

CLBs

最大值

可用

用户 我/o

最大值

差速器

我/o 对

分布式

ram 比特

块

ram 比特

XC2S50E 1,728 23,000 - 50,000 16 x 24 384 182 84 24,576 32K

XC2S100E 2,700 37,000 - 100,000 20 x 30 600 202 86 38,400 40K

XC2S150E 3,888 52,000 - 150,000 24 x 36 864 263 114 55,296 48K

XC2S200E 5,292 71,000 - 200,000 28 x 42 1,176 289 120 75,264 56K

XC2S300E 6,912 93,000 - 300,000 32 x 48 1,536 329 120 98,304 64K