2-7

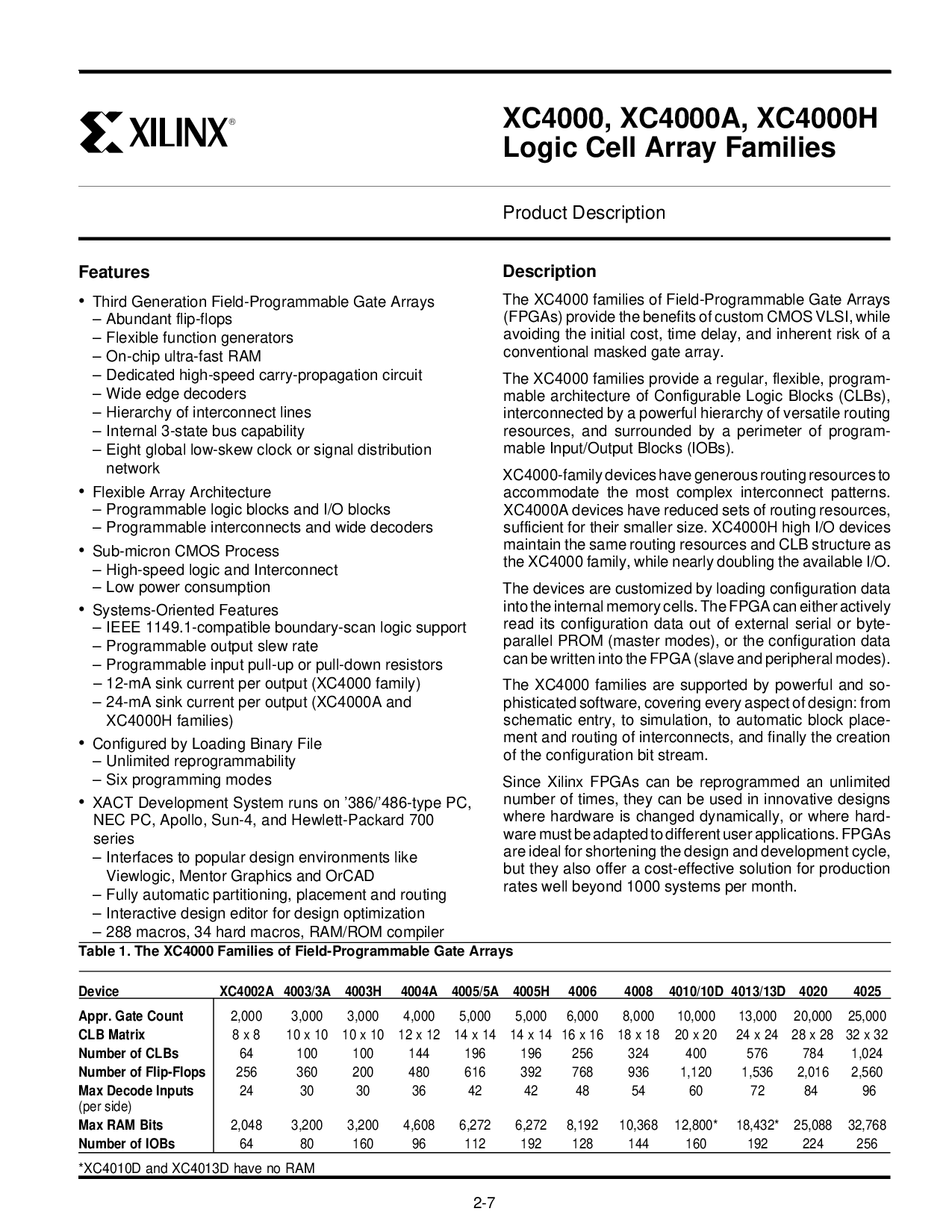

设备 XC4002A 4003/3a 4003H 4004A 4005/5a 4005H 4006 4008 4010/10d 4013/13d 4020 4025

appr. 闸门 计数

2,000 3,000 3,000 4,000 5,000 5,000 6,000 8,000 10,000 13,000 20,000 25,000

clb 矩阵

8 x 8 10 x 10 10 x 10 12 x 12 14 x 14 14 x 14 16 x 16 18 x 18 20 x 20 24 x 24 28 x 28 32 x 32

号码 的 clbs

64 100 100 144 196 196 256 324 400 576 784 1,024

号码 的 人字拖

256 360 200 480 616 392 768 936 1,120 1,536 2,016 2,560

最大值 解码 输入

24 30 30 36 42 42 48 54 60 72 84 96

(按 侧面)

最大值 ram 比特

2,048 3,200 3,200 4,608 6,272 6,272 8,192 10,368 12,800* 18,432* 25,088 32,768

号码 的 iobs

64 80 160 96 112 192 128 144 160 192 224 256

*xc4010d 和 xc4013d 有 否 ram

xc4000, xc4000a, xc4000h

逻辑 细胞 阵列 家庭

产品 描述

描述

这 xc4000 家庭 的 字段-可编程 闸门 阵列

(fpgas) 提供 这 好处 的 自定义 cmos vlsi, 同时

避免 这 初始 成本, 时间 延迟, 和 固有的 风险 的 一个

常规 蒙面 闸门 阵列.

这 xc4000 家庭 提供 一个 常规, 灵活, 程序-

mable 体系结构 的 可配置 逻辑 块 (clbs),

互联互通 由 一个 强大的 层次结构 的 多才多艺 路由

资源, 和 包围 由 一个 周长 的 程序-

mable 输入/输出 块 (iobs).

xc4000-家庭 设备 有 大方 路由 资源 至

容纳 这 大多数 复杂 互连 图案.

xc4000a 设备 有 减少 集 的 路由 资源,

足够 用于 他们的 较小 尺寸. xc4000h 高 我/o 设备

维护 这 相同 路由 资源 和 clb 结构 作为

这 xc4000 家庭, 同时 近 加倍 这 可用 我/o.

这 设备 是 定制 由 正在加载 配置 数据

进入 这 内部 记忆 细胞. 这 fpga 可以 要么 积极

阅读 其 配置 数据 出点 的 外部 串行 或 字节-

平行 舞会 (主人 模式), 或 这 配置 数据

可以 是 书面 进入 这 fpga (奴隶 和 外围设备 模式).

这 xc4000 家庭 是 支持 由 强大的 和 所以-

phisticated 软件, 覆盖 每 方面 的 设计: 从

原理图 进入, 至 仿真, 至 自动 块 地点-

门特 和 路由 的 互连, 和 最后 这 创建

的 这 配置 有点 溪流.

自 xilinx fpgas 可以 是 重新编程 一个 无限

号码 的 次, 他们 可以 是 已使用 入点 创新 设计

在哪里 硬件 是 已更改 动态, 或 在哪里 硬-

商品 必须 是 已适应 至 不同的 用户 应用程序. fpgas

是 理想 用于 缩短 这 设计 和 发展 循环,

但是 他们 也 报价 一个 成本效益 解决方案 用于 生产

费率 井 超越 1000 系统 按 月份.

特点

•

第三 世代 字段-可编程 闸门 阵列

– abundant 人字拖

– 灵活 功能 发电机

– 片上 超-快 ram

– 专用 高速 进位-传播 电路

– 宽 边缘 解码器

– 层次结构 的 互连 线条

– 内部 3-州 总线 能力

– 八 全球 低偏斜 时钟 或 信号 分布

网络

•

灵活 阵列 体系结构

– 可编程 逻辑 块 和 我/o 块

– 可编程 互连 和 宽 解码器

•

亚微米 cmos 流程

– 高速 逻辑 和 互连

– 低 电源 消费

•

系统-面向 特点

– ieee 1149.1-兼容 边界扫描 逻辑 支持

– 可编程 输出 回转 费率

– 可编程 输入 上拉 或 下拉 电阻

– 12-ma 水槽 电流 按 输出 (xc4000 家庭)

– 24-ma 水槽 电流 按 输出 (xc4000a 和

xc4000h 家庭)

•

已配置 由 正在加载 二进制 文件

– 无限 可重新编程性

– 六个 编程 模式

•

xact 发展 系统 运行 开启 ’386/’486-类型 pc,

nec pc, apollo, 太阳-4, 和 hewlett-packard 700

系列

– 接口 至 受欢迎 设计 环境 喜欢

viewlogic, mentor 图形 和 orcad

– 完全 自动 分区, 放置位置 和 路由

– 交互式 设计 编辑 用于 设计 优化

– 288 宏, 34 硬 宏, ram/rom 编译器

表 1. 这 xc4000 家庭 的 字段-可编程 闸门 阵列