十一月 5, 1998 (版本 5.2) 7-83

7

特点

• 低-成本, 注册/门闩 富有, sram 基于

可重新编程 体系结构

-0.5

µ

m 三个-图层 金属 cmos 流程 技术

- 256 至 1936 逻辑 细胞 (3,000 至 23,000 “gates”)

- 价格 竞争对手 与 闸门 阵列

• 系统 水平 特点

- 系统 业绩 超越 50 mhz

- 6 级别 的 互连 层次结构

- VersaRing

™

我/o 接口 用于 管脚-锁定

- 专用 进位 逻辑 用于 高速 算术

功能

- 级联 链条 用于 宽 输入 功能

- 内置 ieee 1149.1 jtag 边界 扫描 测试一下

电路 开启 全部 我/o 针脚

- 内部 3-州 bussing 能力

- 四 专用 低偏斜 时钟 或 信号 分布

nets

• 多才多艺 我/o 和 包装

- 创新 versaring

™

我/o 接口 提供 一个 高

逻辑 细胞 至 我/o 比率, 与 向上 至 244 我/o 信号

- 可编程 输出 回转率 控制 最大化

业绩 和 减少 噪声

- 零 触发器 保持 时间 用于 输入 寄存器 简化了

系统 计时

- 独立 输出 启用 用于 外部 bussing

- 占地面积 兼容性 入点 普通 软件包 内

这 xc5200 系列 和 与 这 xc4000 系列

- 结束 150 设备/包装 组合, 包括

高级 bga, tq, 和 vq 包装 可用

• 完全 支持 由 xilinx 发展 系统

- 自动 地点 和 路线 软件

- 宽 选择 的 pc 和 workstation platforms

- 结束 100 3rd-派对 alliance 接口

- 支持 由 收缩-包装 foundation 软件

描述

这 xc5200 字段-可编程 闸门 阵列 家庭 是

工程 至 交付 低 成本. 建筑物 开启 经历

获得 与 三个 上一个 成功 sram fpga fami-

谎言, 这 xc5200 家庭 带来 一个 坚固耐用 功能 设置 至 专业版-

可重 逻辑 设计. 这 versablock

™

逻辑 模块,

这 versaring 我/o 接口, 和 一个 富有 层次结构 的 国际米兰-

连接 资源 联合收割机 至 增强 设计 灵活性

和 减少 时间-至-市场. 完成 支持 用于 这

xc5200 家庭 是 已交付 通过 这 熟悉 xilinx 软-

商品 环境. 这 xc5200 家庭 是 完全 支持 开启

受欢迎 workstation 和 pc platforms. 受欢迎 设计

进入 方法 是 完全 支持, 包括 abel, sche-

马蒂奇 捕获, vhdl, 和 verilog hdl 合成. 设计-

ers 利用 逻辑 合成 可以 使用 他们的 现有 工具 至

设计 与 这 xc5200 设备.

.

0

xc5200 系列

字段 可编程 闸门 阵列

十一月 5, 1998 (版本 5.2)

07*

产品 规格

右

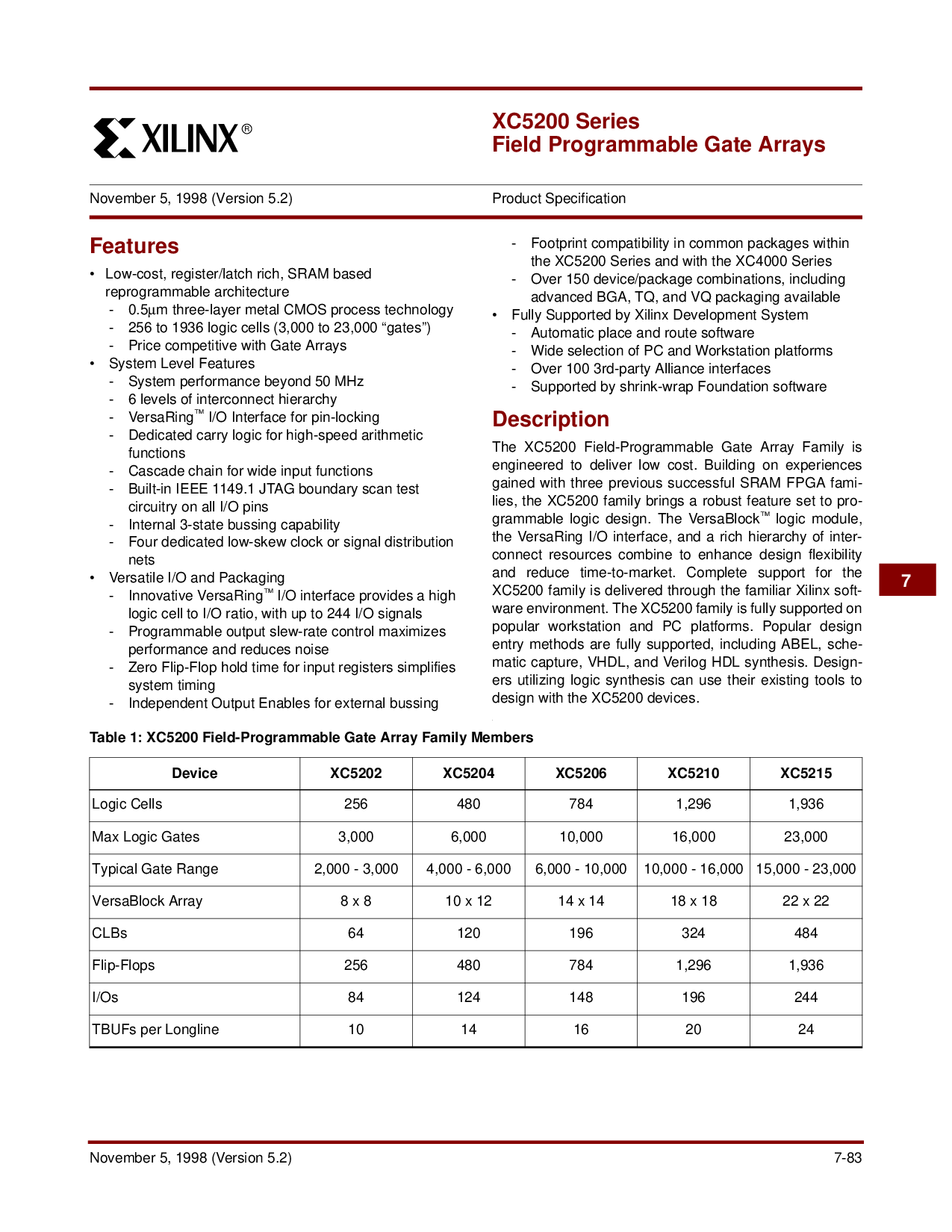

表 1: xc5200 字段-可编程 闸门 阵列 家庭 成员

设备 XC5202 XC5204 XC5206 XC5210 XC5215

逻辑 细胞 256 480 784 1,296 1,936

最大值 逻辑 盖茨 3,000 6,000 10,000 16,000 23,000

典型 闸门 范围 2,000 - 3,000 4,000 - 6,000 6,000 - 10,000 10,000 - 16,000 15,000 - 23,000

versablock 阵列 8 x 8 10 x 12 14 x 14 18 x 18 22 x 22

CLBs 64 120 196 324 484

人字拖 256 480 784 1,296 1,936

我/操作系统 84 124 148 196 244

tbufs 按 longline 1014162024