ds017 (v1.6) january 8, 2002

www.xilinx.com

1

产品 规格

1-800-255-7778

© 2002 xilinx, 公司 全部 权利 保留. 全部 xilinx 商标, 已注册 商标, patents, 和 免责声明 是 作为 已列出 一个t

http://www.xilinx.com/法律.htm

.

全部 其他 商标 和 已注册 商标 是 这 财产 的 他们的 各自 业主. 全部 规格 是 主题 至 change 无 通知.

特点

• 最低 电源 64 宏单元 cpld

• 6.0 ns pin-to-pin 逻辑 延误

• 系统 频率 向上 至 145 mhz

• 64 宏单元 与 1,500 可用 盖茨

• 可用 入点 小 占地面积 软件包

- 44-管脚 plcc (36 用户 我/o 针脚)

- 44-管脚 vqfp (36 用户 我/o 针脚)

- 48-球 cs bga (40 用户 我/o 针脚)

- 56-球 cp bga (48 用户 我/o 针脚)

- 100-管脚 vqfp (68 用户 我/o 针脚)

• 优化 用于 3.3v 系统

- 超-低 电源 操作

- 5v 宽容 我/o 针脚 与 3.3v 核心 供应

- 高级 0.35 微米 五个 图层 金属 可擦可编程只读存储器

流程

- 快 零 power™ (fzp) cmos 设计

技术

• 高级 系统 特点

- 在系统内 编程

- 输入 寄存器

- 可预测 计时 型号

- 向上 至 23 可用 时钟 按 功能 块

- 优秀 管脚 保留 期间 设计 变更

- 已满 ieee 标准 1149.1 边界扫描 (jtag)

- 四 全球 时钟

- 八 产品 期限 控制 条款 按 功能 块

• 快 isp 编程 次

• 港口 启用 管脚 用于 双 功能 的 jtag isp 针脚

• 2.7v 至 3.6v 供应 电压 在 工业 温度

ran通用电气

• 可编程 回转 费率 控制 按 宏单元

• 安全 有点 防止 未经授权 访问权限

• 参考 至 xpla3 家庭 数据 工作表 (

DS012

) 用于

体系结构 描述

描述

这 xcr3064xl 是 一个 3.3v, 64-宏单元 cpld 有针对性的 在

电源 敏感 设计 那 需要 领先 边缘 程序-

mable 逻辑 解决方案. 一个 合计 的 四 功能 块 提供

1,500 可用 盖茨. pin-to-pin 传播 延误 是

6.0 ns 与 一个 最大值 系统 频率 的 145 mhz.

totalcmos 设计 技术 用于 快

零 电源

xilinx 优惠 一个 totalcmos cpld, 两者都有 入点 流程 技术-

ogy 和 设计 技术. xilinx 雇用 一个 级联 的

cmos 盖茨 至 实施 其 总金额 的 产品 相反 的

这 传统 感觉 放大器 方法. 这个 cmos 闸门 imple-

心理状态 允许 xilinx 至 报价 cplds 那 是 两者都有 高

业绩 和 低 电源, 断裂 这 范式 那 至

有 低 电源, 你 必须 有 低 业绩. 参考 至

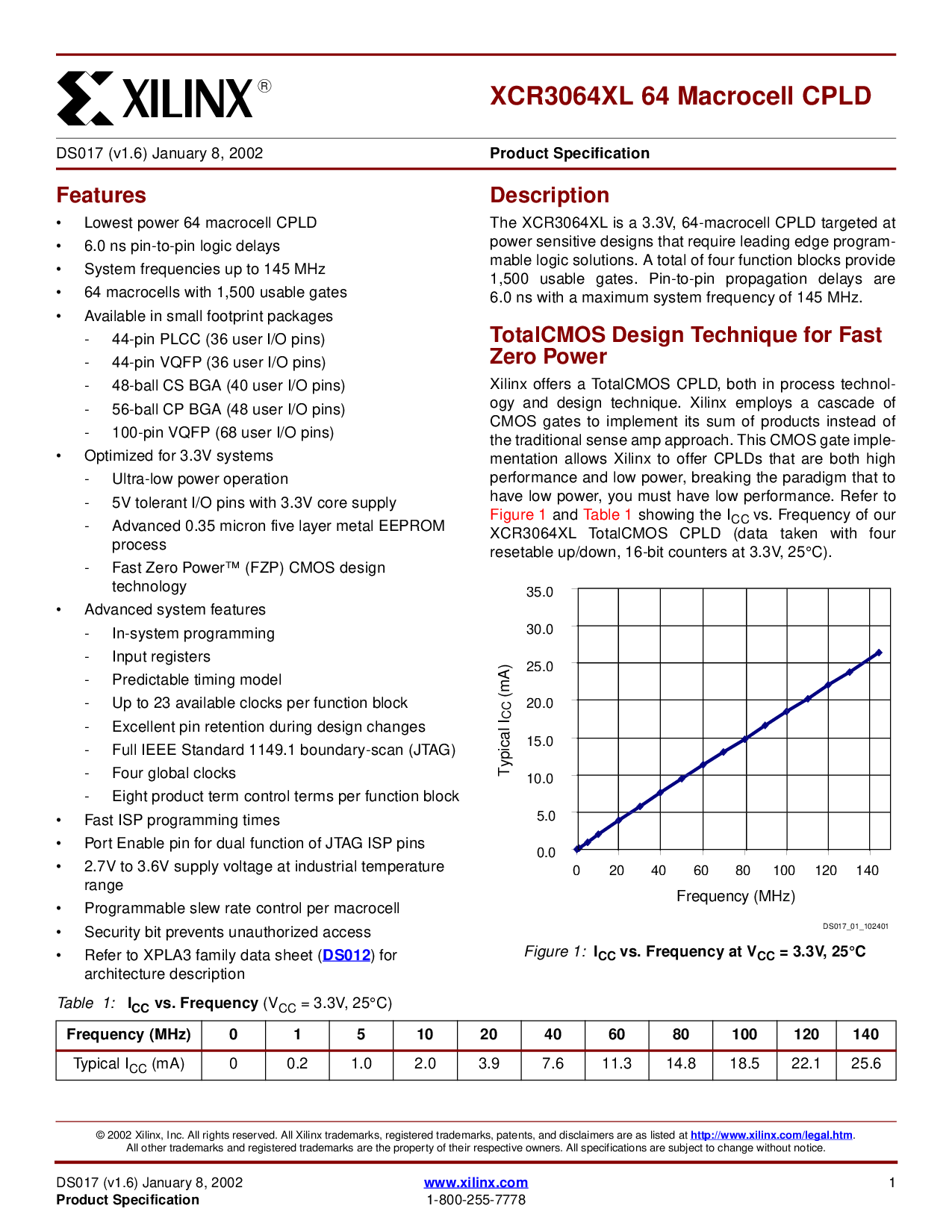

图 1和表 1显示 这 我

抄送

vs. 频率 的 我们的

xcr3064xl totalcmos cpld (数据 已拍摄 与 四

可重置 向上/向下, 16-有点 计数器 在 3.3v, 25

°

c).

0

xcr3064xl 64 宏单元 cpld

ds017 (v1.6) january 8, 2002

014

产品 规格

右

图 1:

我

抄送

vs. 频率 在 v

抄送

= 3.3v, 25°c

0.0

5.0

10.0

15.0

20.0

25.0

30.0

35.0

0 20 40 60 80 100 120 140

频率 (mhz)

DS017_01_102401

典型 我

抄送

(ma)

表 1:

我

抄送

vs. 频率

(v

抄送

= 3.3v, 25

°

c)

频率 (mhz) 0 1 5 10 20 40 60 80 100 120 140

Ty p 我c 一个 l 我

抄送

(ma) 0 0.2 1.0 2.0 3.9 7.6 11.3 14.8 18.5 22.1 25.6