7-89

注意事项: 这些 设备 是 敏感 至 静电 放电; 跟着 适当的 集成电路 搬运 程序.

1-888-intersil 或 321-724-7143 | 版权 © intersil 公司 1999

CD4015BMS

cmos 双 4-舞台 静态 轮班 注册

与 串行 输入/平行 输出

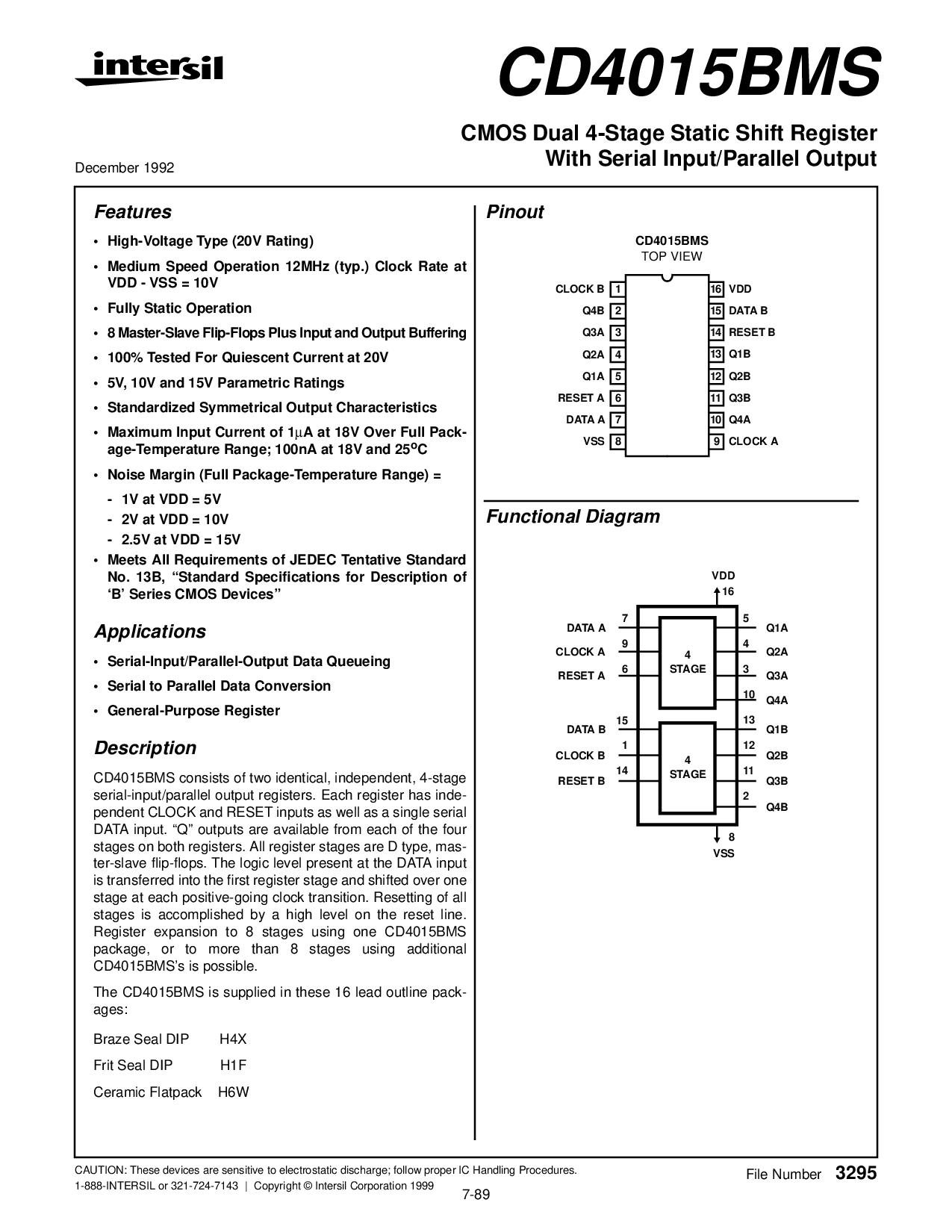

引出线

CD4015BMS

顶部 查看

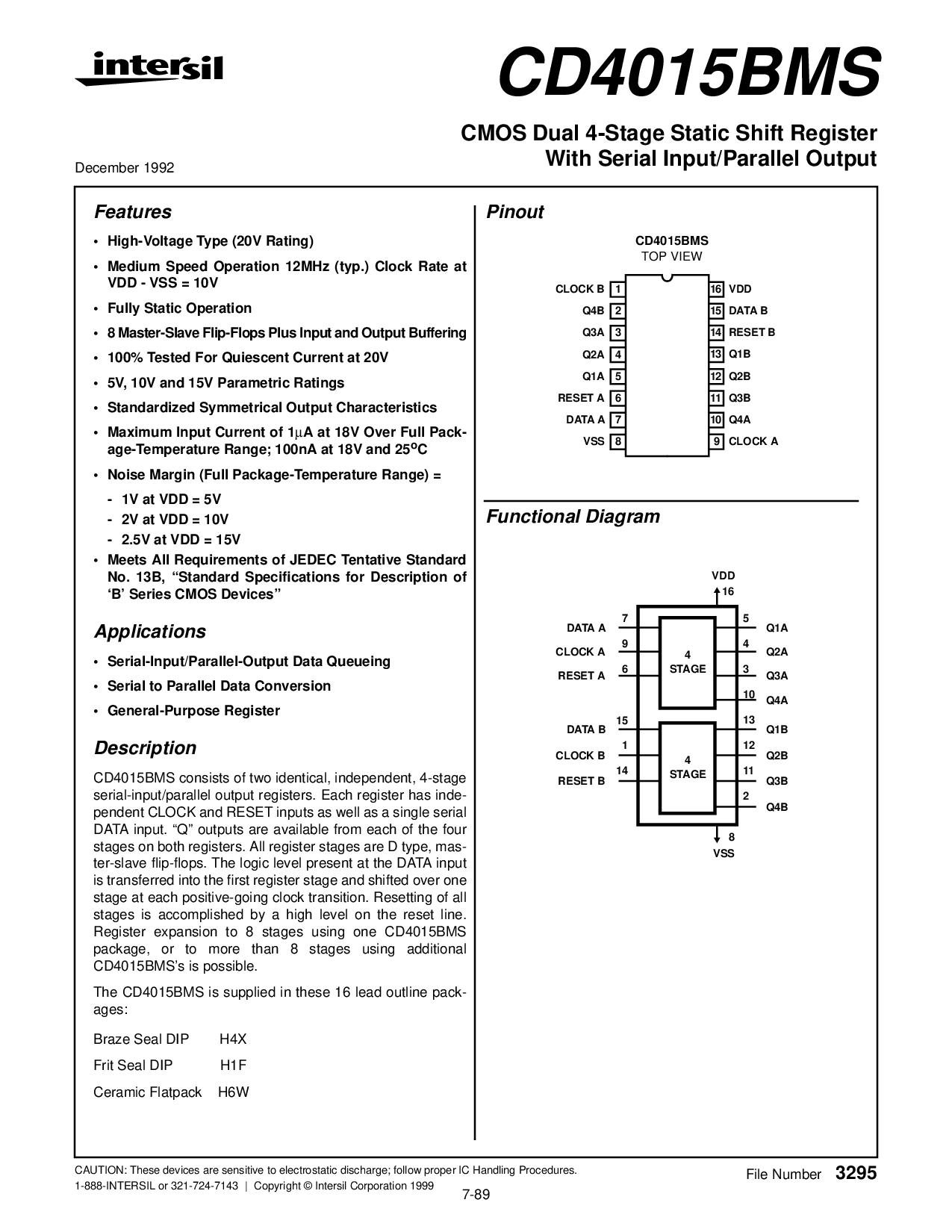

功能 图表

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

时钟 b

Q4B

Q3A

Q2A

Q1A

重置 一个

vss

数据 一个

VDD

重置 b

Q1B

Q2B

Q3B

Q4A

时钟 一个

数据 b

数据 一个

时钟 一个

重置 一个

数据 b

时钟 b

重置 b

Q1A

Q2A

Q3A

Q4A

Q1B

Q2B

Q3B

Q4B

vss

VDD

7

9

6

15

1

14

5

4

3

10

13

12

11

2

16

8

4

舞台

4

舞台

特点

• 高电压 类型 (20v 评级)

• 中 速度 操作 12mhz (典型值.) 时钟 费率 在

vdd - vss = 10v

• 完全 静态 操作

• 8 主从 人字拖 加号 输入 和 输出 缓冲

• 100% 已测试 用于 静态 电流 在 20v

• 5v, 10v 和 15v 参数化 额定值

• 标准化 对称 输出 特性

• 最大值 输入 电流 的 1

µ

一个 在 18v 结束 已满 空调组件-

年龄-温度 范围; 100na 在 18v 和 25

o

c

• 噪声 边距 (已满 包装-温度 范围) =

- 1v 在 vdd = 5v

- 2v 在 vdd = 10v

- 2.5v 在 vdd = 15v

• 满足 全部 要求 的 电子元件工业联合会 tentative 标准

否. 13b, “standard 特定 用于 描述 的

‘b’ 系列 cmos devices”

应用程序

• 串行-输入/平行-输出 数据 排队

• 串行 至 平行 数据 换算

• 通用 注册

描述

cd4015bms 由 的 两个 相同, 独立, 4-舞台

串行-输入/平行 输出 寄存器. 每个 注册 有 inde-

悬挂式 时钟 和 重置 输入 作为 井 作为 一个 单独 串行

数据 输入. “q” 产出 是 可用 从 每个 的 这 四

阶段 开启 两者都有 寄存器. 全部 注册 阶段 是 d 类型, mas-

之三-奴隶 flip-fl. 这 逻辑 水平 目前 在 这 数据 输入

是 已转移 进入 这 first 注册 舞台 和 换档 结束 一个

舞台 在 每个 积极向上 时钟 过渡. 重置 的 全部

阶段 是 已完成 由 一个 高 水平 开启 这 重置 线.

注册 扩展 至 8 阶段 使用 一个 cd4015bms

包装, 或 至 更多 比 8 阶段 使用 附加

cd4015bms’s 是 可能.

这 cd4015bms 是 提供的 入点 这些 16 铅 大纲 空调组件-

年龄:

braze 密封 倾角 H4X

玻璃料 密封 倾角 H1F

陶瓷 扁平包装 H6W

12月 1992

文件 号码

3295