©2000 综合 设备 技术, 公司

dsc-2944/8

1

idt70v25s/l

高速 3.3v

8k x 16 双端口

静态 ram

◆◆

◆◆

◆

idt70v25 很容易 展开 数据 总线 宽度 至 32 比特 或 更多

使用 这 主人/奴隶 选择 当 层叠 更多 比

一个 设备

◆◆

◆◆

◆

m/

s

= v

ih

用于

忙

输出 旗子 开启 主人

m/

s

= v

il

用于

忙

输入 开启 奴隶

◆◆

◆◆

◆

忙

和 中断 旗子

◆◆

◆◆

◆

片上 港口 仲裁 逻辑

◆◆

◆◆

◆

已满 片上 硬件 支持 的 信号量 信令

之间 端口

◆◆

◆◆

◆

完全 异步 操作 从 要么 港口

◆◆

◆◆

◆

lvttl-兼容, 单独 3.3v (±0.3v) 电源 供应

◆◆

◆◆

◆

可用 入点 84-管脚 pga, 84-管脚 plcc 和 100-管脚 tqfp

◆◆

◆◆

◆

工业 温度 范围 (-40°c 至 +85°c) 是 可用

用于 已选择 速度

备注:

1. (主人):

忙

是 输出; (奴隶):

忙

是 输入.

2.

忙

产出 和

智力

产出 是 非-三-声明 按压-拉.

◆◆

◆◆

◆

真 双端口 记忆 细胞 哪个 允许 同时

读取 的 这 相同 记忆 位置

◆◆

◆◆

◆

高速 访问权限

– 商业: 15/20/25/35/55ns (最大值.)

– 工业: 20/25/35/55ns (最大值.)

◆◆

◆◆

◆

低功耗 操作

– IDT70V25S

活动: 400mw (典型值.)

备用: 3.3mw (典型值.)

– IDT70V25L

活动: 380mw (典型值.)

备用: 660

µ

w (典型值.)

◆◆

◆◆

◆

分开 高字节 和 下部-字节 控制 用于 多路复用

总线 兼容性

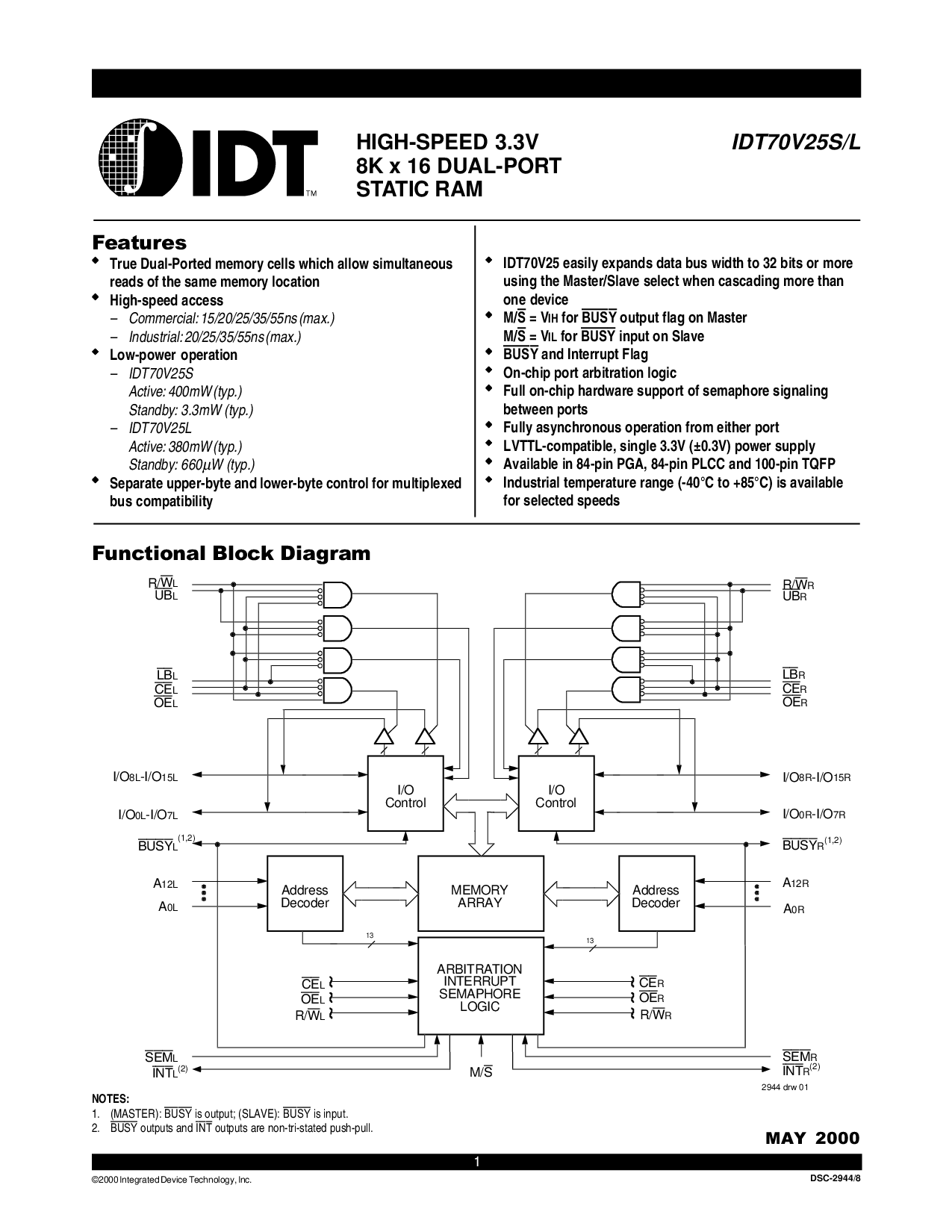

我/o

控制

地址

解码器

记忆

阵列

仲裁

中断

信号量

逻辑

地址

解码器

我/o

控制

右/

w

l

忙

l

一个

12L

一个

0L

2944 drw 01

ub

l

磅

l

ce

l

oe

l

我/o

8L

-我/o

15L

我/o

0L

-我/o

7L

ce

l

oe

l

右/

w

l

SEM

l

智力

l

m/

s

右/

w

右

忙

右

ub

右

磅

右

ce

右

oe

右

我/o

8R

-我/o

15R

我/o

0R

-我/o

7R

一个

12R

一个

0R

右/

w

右

SEM

右

智力

右

ce

右

oe

右

(2)

(1,2)

(1,2)

(2)

13

13

,