管脚 功能

g

t

ttl 接地 (0v)

v

t

ttl v

抄送

(+5.0v)

v

e?

ecl v

抄送

(+5.0v)

g

e?

ecl 接地 (0v)

d, d 信号 输入 (pecl)

v

bb

v

bb

参考 输出 (pecl)

q

0

- q

3

信号 产出 (ttl)

en 启用 输入 (pecl)

描述

特点

ClockWorks™

SY10H842

SY100H842

■

翻译 正 ecl-至-ttl (pecl-至-ttl)

■

300ps pin-to-pin 偏斜

■

500ps 零件对零件 偏斜

■

差速器 内部 设计 用于 增加 噪声

免疫 和 稳定 阈值 输入

■

v

bb

参考 输出

■

单独 供应

■

启用 输入

■

额外的 ttl 和 ecl 电源/接地 针脚 至 减少

十字形-谈话/噪声

■

高 驱动器 能力: 24ma 每个 输出

■

完全 兼容 与 行业 标准 10k, 100k

我/o 级别

■

可用 入点 16-管脚 soic 包装

这 sy10/100h842 是 单独 供应, 低 偏斜

翻译 1:4 时钟 驱动程序.

这 设备 功能 一个 24ma ttl 输出 舞台, 与

交流电 业绩 指定 进入 一个 50pf 荷载 电容.

一个 高 开启 这 启用 管脚 (en) 力 全部 产出 低.

作为 频率 增加 至 40mhz 和 以上, 精确

计时 和 整形 的 时钟 信号 成为 极其

重要. 这 h842 解决方案 几个 时钟 分布

问题 这样的 作为 最小化 偏斜 300ps), 最大化

时钟 扇出 (24ma 驱动器), 和 精确 职责 循环 控制

通过 一个 专有 差速器 内部 设计.

这 10k 版本 是 兼容 与 10kh ecl 逻辑

级别. 这 100k 版本 是 兼容 与 100k 级别.

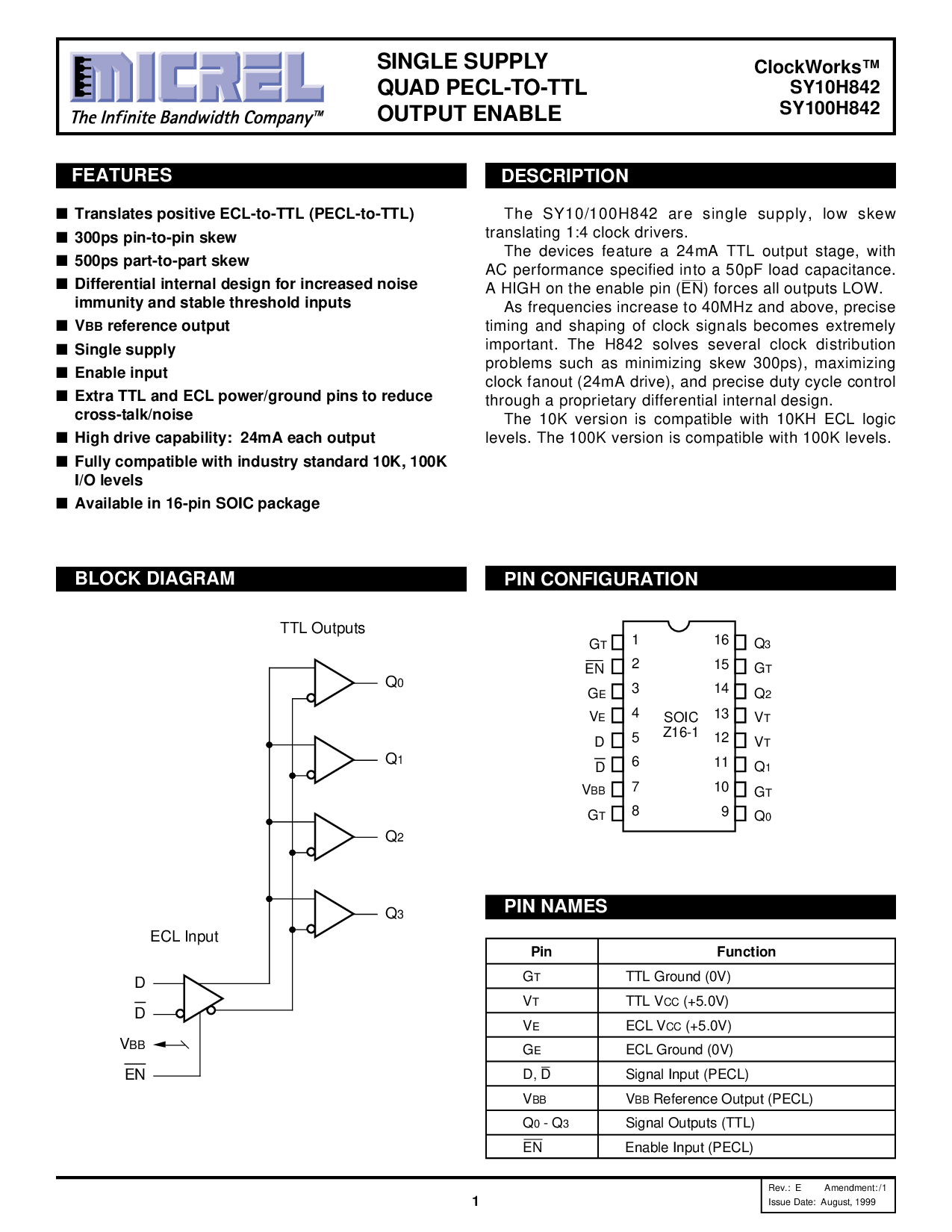

管脚 配置

单独 供应

四边形 pecl-至-ttl

输出 启用

管脚 姓名

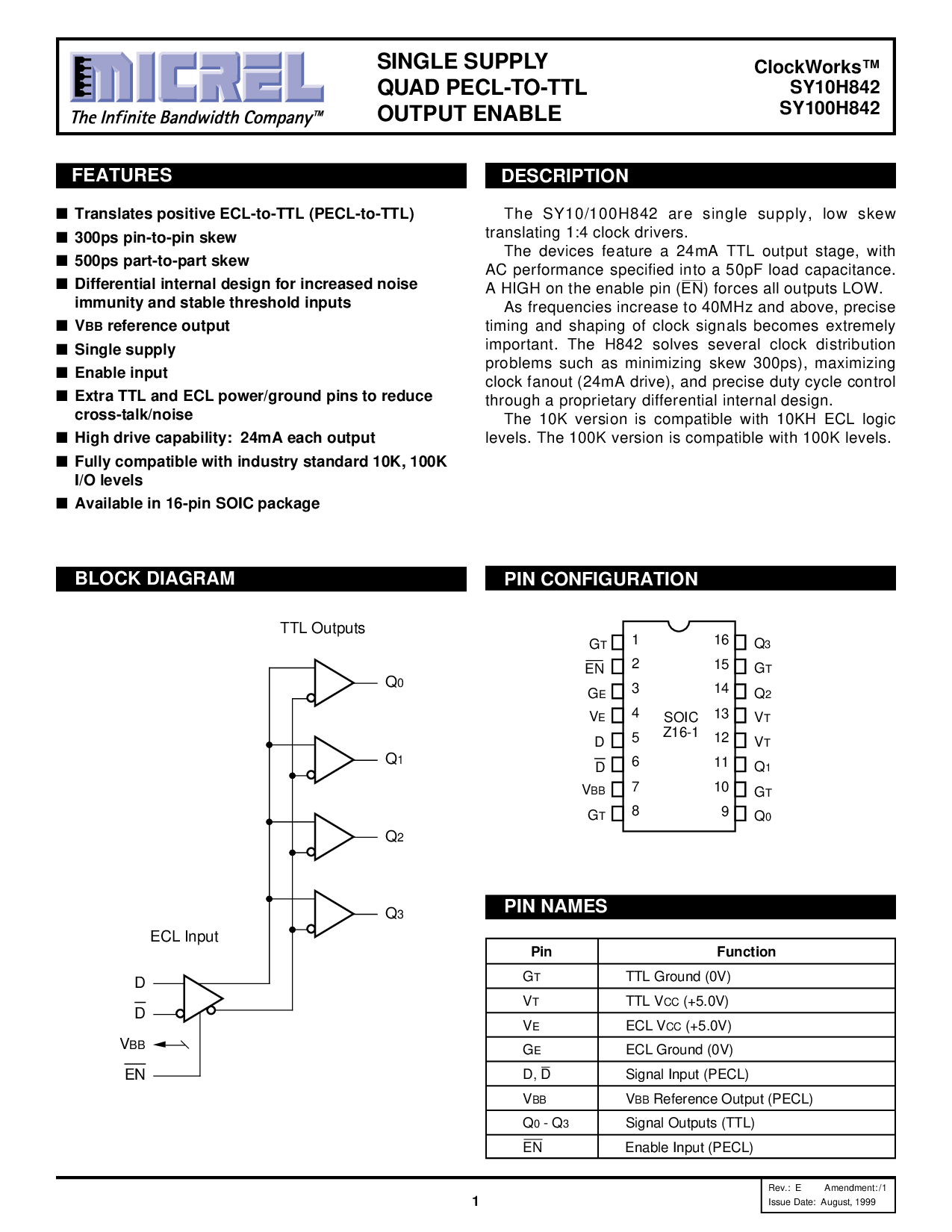

块 图表

d

d

q

0

q

1

q

2

q

3

v

bb

en

ecl 输入

ttl 产出

rev.: e? 修正案: /1

问题 日期: 8月, 1999

g

t

q

3

SOIC

z16-1

116

g

t

2

15

g

e?

q

2

314

v

e?

v

t

4

13

v

t

512

q

1

6

11

v

bb

g

t

710

g

t

q

0

8

9

en

d

d

1