motorola cmos 逻辑 数据

1

mc14597b mc14598b

8-位 总线-兼容 Latches

这mc14597b 和 mc14598b 是 8–bit latches, 一个 addressed 和 一个

内部的计数器 和 这 其它 addressed 和 一个外部 二进制的 地址.

这8 latch–outputs是 高 驱动, three–state 和 总线 线条 兼容. 这

驱动能力 准许 直接 产品 和 mpu 系统 此类 作 这

motorola 6800 家族.

和mc14597b, 一个 3–bit 地址 计数器 (clocked 在 这 下落 边缘 的

increment)选择 这 适合的 获得. 这 latches 的 这 mc14598b 是

accessed通过 这 地址 管脚, a0, a1, 和 a2. 一个 全部

标记 是 提供 在

这 mc14597b 至 表明 这 位置 的 这 地址 计数器.

所有8 输出 从 这 latches 是 有 在 并行的 当 使能是 在 这

低状态. 数据 是 entered 在 一个 选择 获得 从这 数据 管脚 当 这

strobe 是 高. 主控 重置 是 有 在 两个都 部分.

•

串行 数据 输入

•

three–state 总线 兼容 并行的 输出

•

three–state 控制 管脚 (使能

) ttl 兼容 输入

•

打开 流 全部

标记 (多样的 获得 wire–o 环绕)

•

主控 重置

•

水平的 shifting 输入 在 所有 除了 使能

•

二极管 保护 — 所有 输入

•

供应 电压 范围 — 3.0 vdc 至 18 vdc

•

有能力 的 驱动 ttl 在 评估 温度 范围

和 输出 作 跟随:

1 ttl 加载

4 lsttl 负载

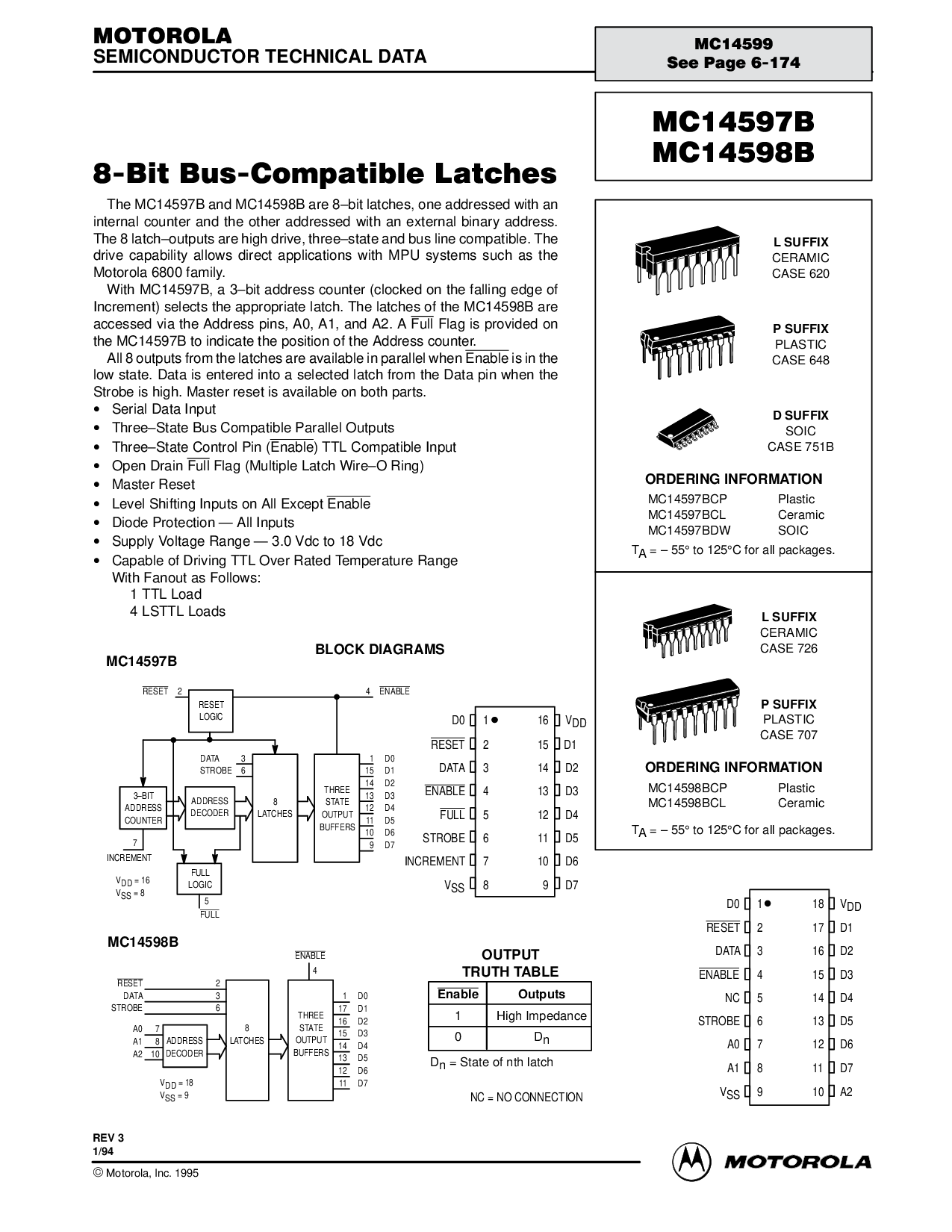

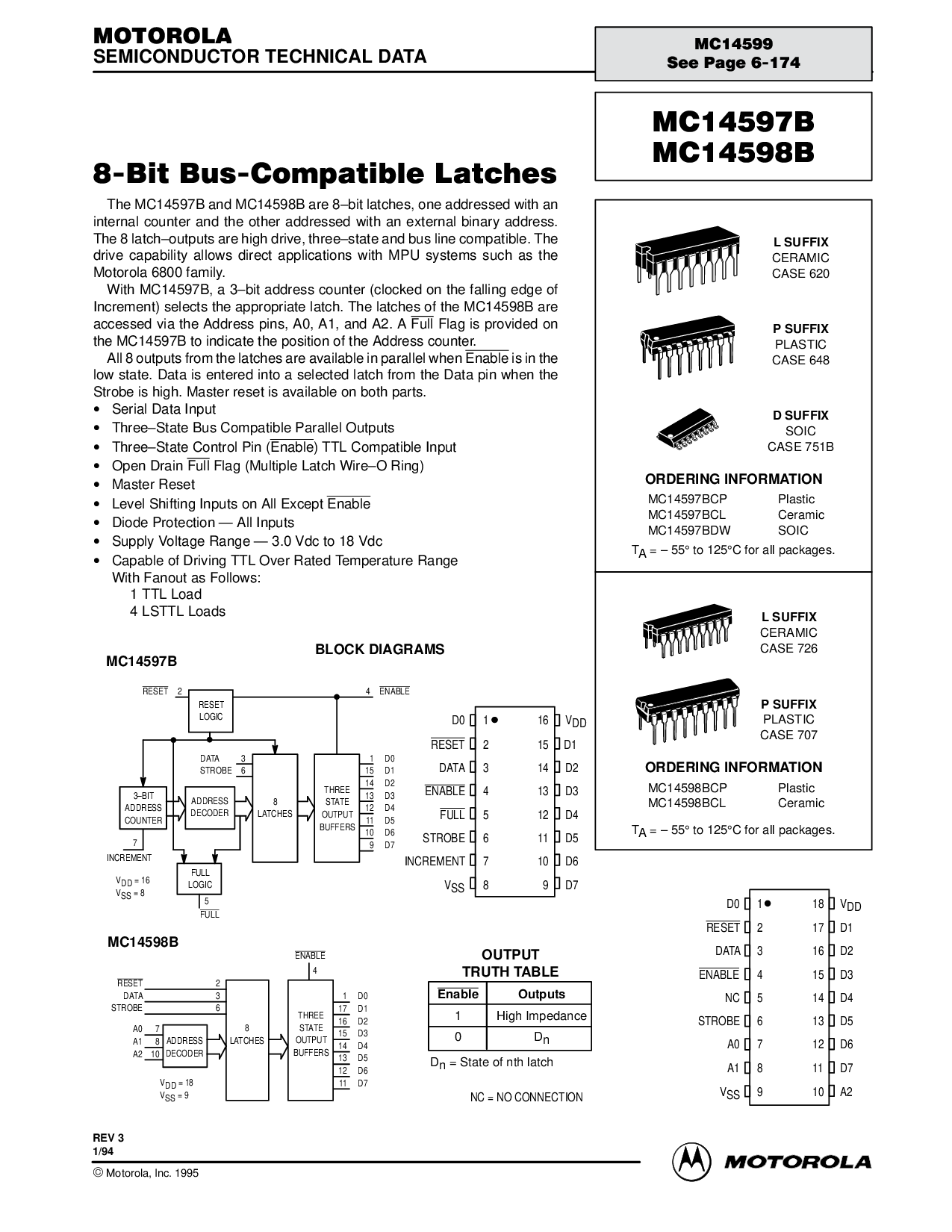

块 图解

MC14598B

MC14597B

使能 输出

1 高 阻抗

0 D

n

D

n

= 状态 的 nth 获得

输出

真实 表格

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

D4

D3

D2

D1

V

DD

D7

D6

D5

使能

数据

重置

D0

V

SS

INCREMENT

STROBE

全部

NC

数据

重置

D0

V

SS

A1

A0

STROBE

使能

D3

D2

D1

V

DD

A2

D7

D6

D5

D4

14

15

16

17

18

10

11

12

13

5

4

3

2

1

9

8

7

6

nc = 非 连接

三

状态

输出

缓存区

8

LATCHES

地址

解码器

3–BIT

地址

计数器

全部

逻辑

重置

逻辑

重置

2 4 使能

1

15

14

13

12

11

10

9

D0

D1

D2

D3

D4

D5

D6

D7

数据 3

STROBE 6

INCREMENT

5

全部

V

DD

= 16

V

SS

= 8

7

1

17

16

15

14

13

12

11

D0

D1

D2

D3

D4

D5

D6

D7

使能

4

三

状态

输出

缓存区

8

LATCHES

地址

解码器

V

DD

= 18

V

SS

= 9

2

3

6

重置

数据

STROBE

A0

A1

A2

7

8

10

MOTOROLA

半导体 技术的 数据

motorola, 公司 1995

rev 3

1/94

MC14599

看 页 6-174

MC14597B

MC14598B

l 后缀

陶瓷的

情况 620

订货 信息

MC14597BCP 塑料

MC14597BCL 陶瓷的

MC14597BDW SOIC

T

一个

= – 55

°

至 125

°

c 为 所有 包装.

p 后缀

塑料

情况 648

d 后缀

SOIC

情况 751b

l 后缀

陶瓷的

情况 726

p 后缀

塑料

情况 707

订货 信息

MC14598BCP 塑料

MC14598BCL 陶瓷的

T

一个

= – 55

°

至 125

°

c 为 所有 包装.