低成本 3.3v 零 延迟 缓冲区

CY2305

CY2309

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07140 rev. *c 修订 12月 14, 2002

特点

• 10-mhz 至 100-/133-mhz 操作 范围, 兼容

与 cpu 和 pci 总线 频率

• 零 输入-输出 传播 延迟

• 多个 低偏斜 产出

— 输出-输出 偏斜 较少 比 250 ps

— 设备-设备 偏斜 较少 比 700 ps

— 一个 输入 驱动器 五个 产出 (cy2305)

— 一个 输入 驱动器 九 产出, 分组 作为 4 + 4 + 1

(cy2309)

• 较少 比 200 ps 循环-循环 抖动, 兼容 与

Pentium

-基于 系统

• 测试一下 模式 至 旁路 锁相 回路 (pll) (cy2309

仅 [see “select 输入 decoding” 开启 第页 2])

• 可用 入点 节省空间 16-管脚 150-密耳 soic 或

4.4-mm tssop 软件包 (cy2309), 和 8-管脚, 150-密耳

soic 包装 (cy2305)

• 3.3v 操作

• 工业 温度 可用

功能 描述

这 cy2309 是 一个 低成本 3.3v 零 延迟 缓冲区 设计 至

分发 高速 时钟 和 是 可用 入点 一个 16-管脚 soic

或 tssop 包装. 这 cy2305 是 一个 8-管脚 版本 的 这

cy2309. 它 接受 一个 参考 输入, 和 驱动器 出点 五个

低偏斜 时钟. 这 -1h 版本 的 每个 设备 操作 在

向上 至 100-/133-mhz 频率, 和 有 较高 驱动器 比

这 -1 设备. 全部 零件 有 片上 plls 哪个 锁 至 一个

输入 时钟 开启 这 参考 管脚. 这 pll 反馈 是 片上 和

是 获得 从 这 clkout 衬垫.

这 cy2309 有 两个 银行 的 四 产出 每个, 哪个 可以

是 受控 由 这 选择 输入 作为 显示 入点 这

“

选择 输入

解码

”

表 开启 第页 2. 如果 全部 输出 时钟 是 不 必填项,

bankb 可以 是 三个-声明. 这 选择 输入 也 允许 这

输入 时钟 至 是 直接 已应用 至 这 产出 用于 芯片 和

系统 测试 目的.

这 cy2305 和 cy2309 plls 输入 一个 掉电 模式

当 那里 是 否 上升 边缘 开启 这 参考 输入. 入点 这个 州,

这 产出 是 三态 和 这 pll 是 翻转 关, 结果

入点 较少 比 12.0

µ

一个 的 电流 绘制 用于 商业 脾气-

ature 设备 和 25.0

µ

一个 用于 工业 温度 零件. 这

cy2309 pll 关闭 向下 入点 一个 附加 案例 作为 显示 入点

这 表 下面.

多个 cy2305 和 cy2309 设备 可以 接受 这 相同

输入 时钟 和 分发 它. 入点 这个 案例, 这 偏斜 之间 这

产出 的 两个 设备 是 保证 至 是 较少 比 700 ps.

全部 产出 有 较少 比 200 ps 的 循环-循环 抖动. 这 输入

至 输出 传播 延迟 开启 两者都有 设备 是 保证 至

是 较少 比 350 ps, 和 这 输出 至 输出 偏斜 是

保证 至 是 较少 比 250 ps.

这 cy2305/cy2309 是 可用 入点 两个/三个 不同的 配置-

urations, 作为 显示 入点 这 订购 信息 (第页 10). 这

cy2305-1/cy2309-1 是 这 底座 零件. 这 cy2305-1h/

cy2309-1h 是 这 高驱动 版本 的 这 -1, 和 其 上升 和

坠落 次 是 很多 更快 比 这 -1s.

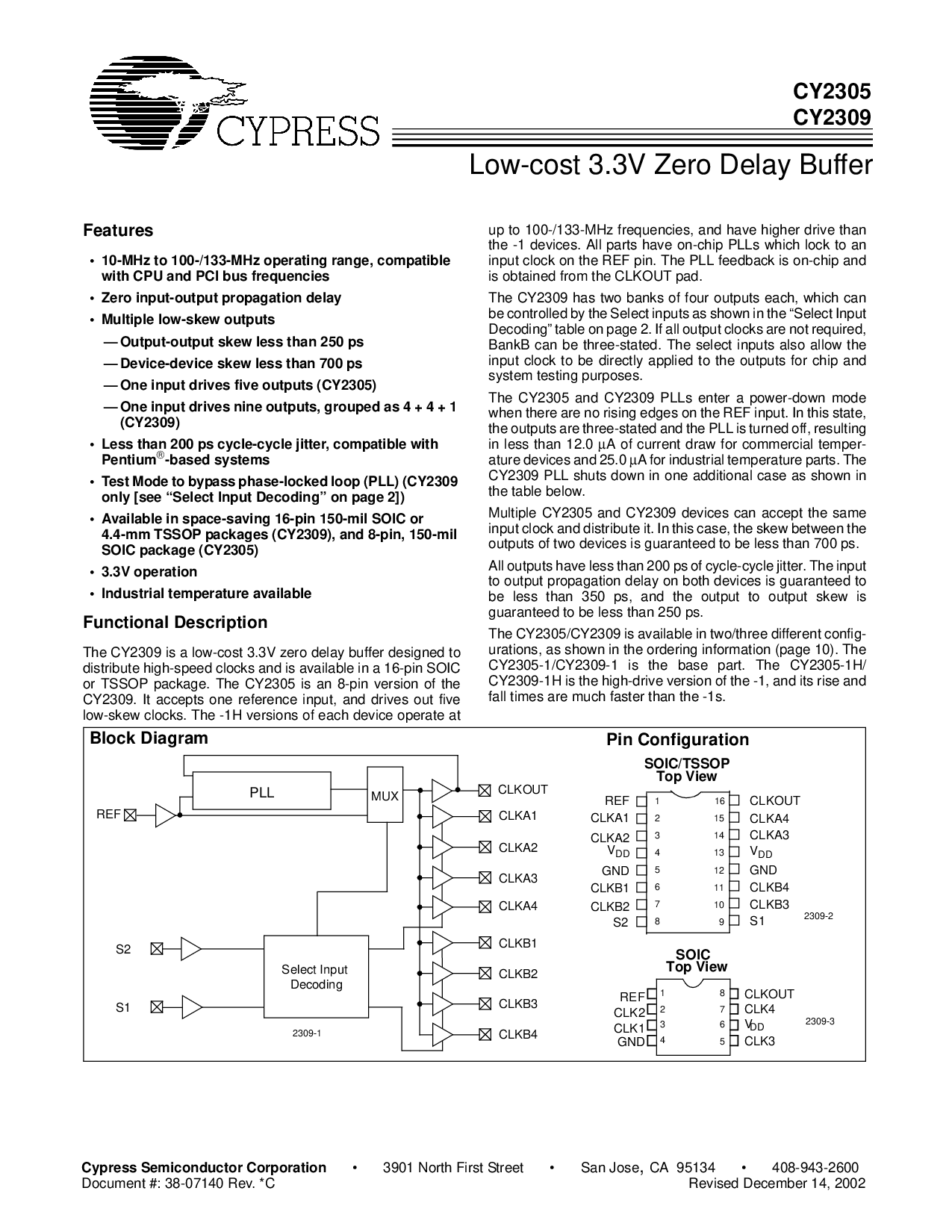

块 图表

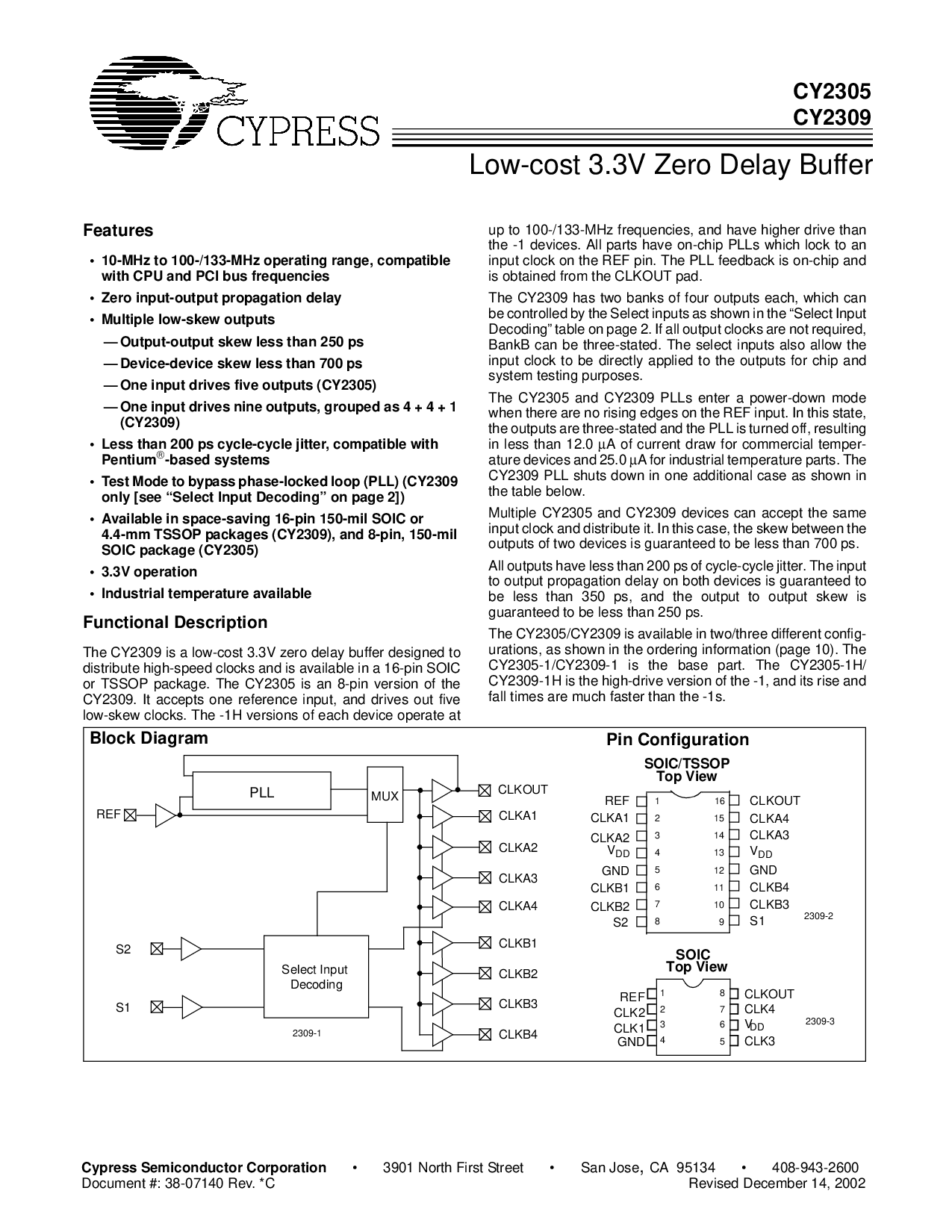

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

参考

CLKA1

CLKA2

v

dd

地

CLKB1

CLKB2

S2

CLKOUT

CLKA4

CLKA3

v

dd

地

CLKB4

CLKB3

S1

soic/tssop

顶部 查看

管脚 配置

2309-1

2309-2

1

2

3

4

5

8

7

6

参考

CLK2

CLK1

地

v

dd

CLKOUT

CLK4

CLK3

SOIC

顶部 查看

2309-3

PLL

mux

选择 输入

参考

S2

S1

CLKA1

CLKA2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

解码

CLKOUT