1

备注:

1. 用于 lcc/plcc 仅: 针脚 1 和 17 是 普通 和 系紧 至 这 模具 atĆ

tach 衬垫. 他们 应该 不 是 已使用.

柏树 半导体 公司

d

3901 北 第一 街道

d

San Jose

d

ca95134

d

408-943-2600

十一月 1994

初步

CY27H512

64K x 8 HighĆSpeed CMOS

非易失存储器

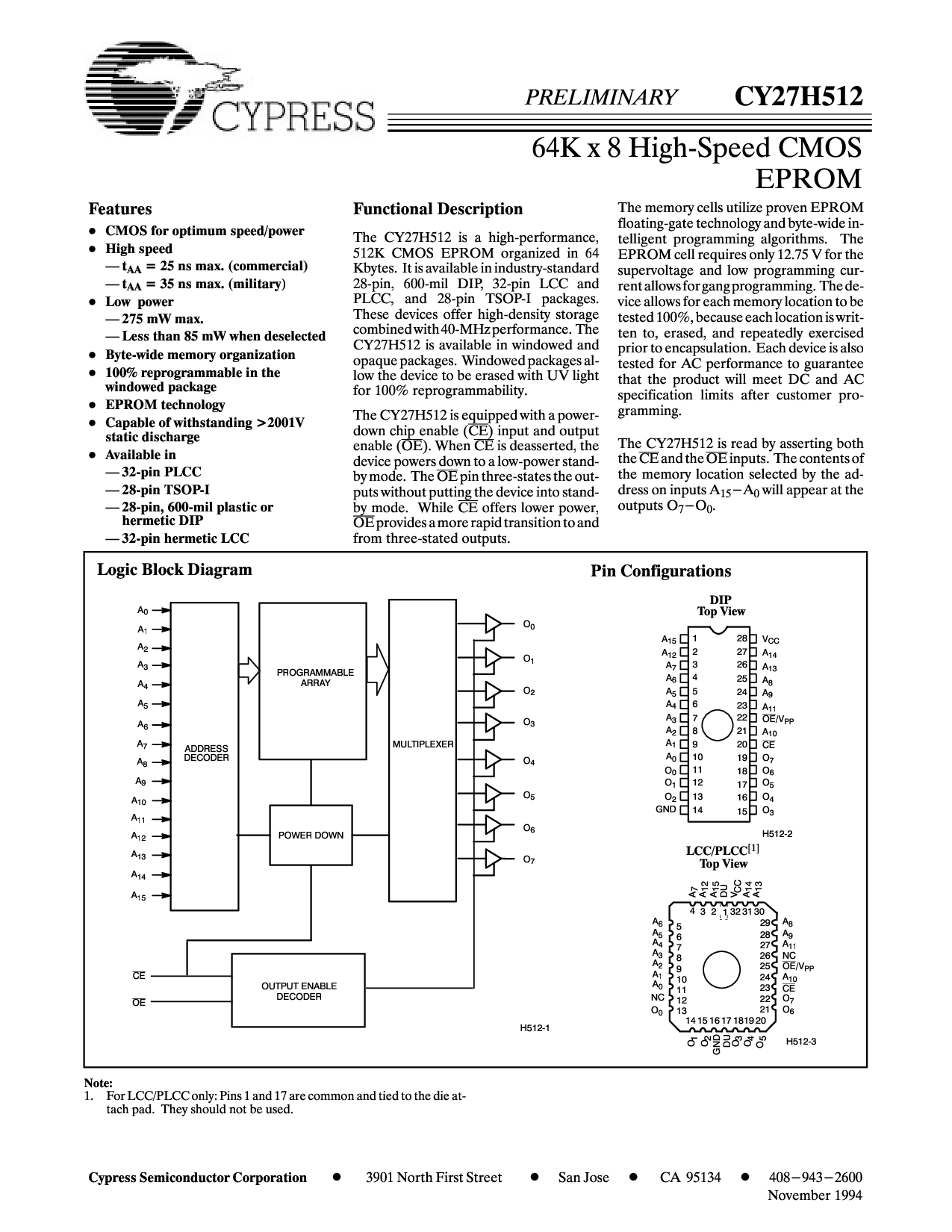

逻辑 块 图表

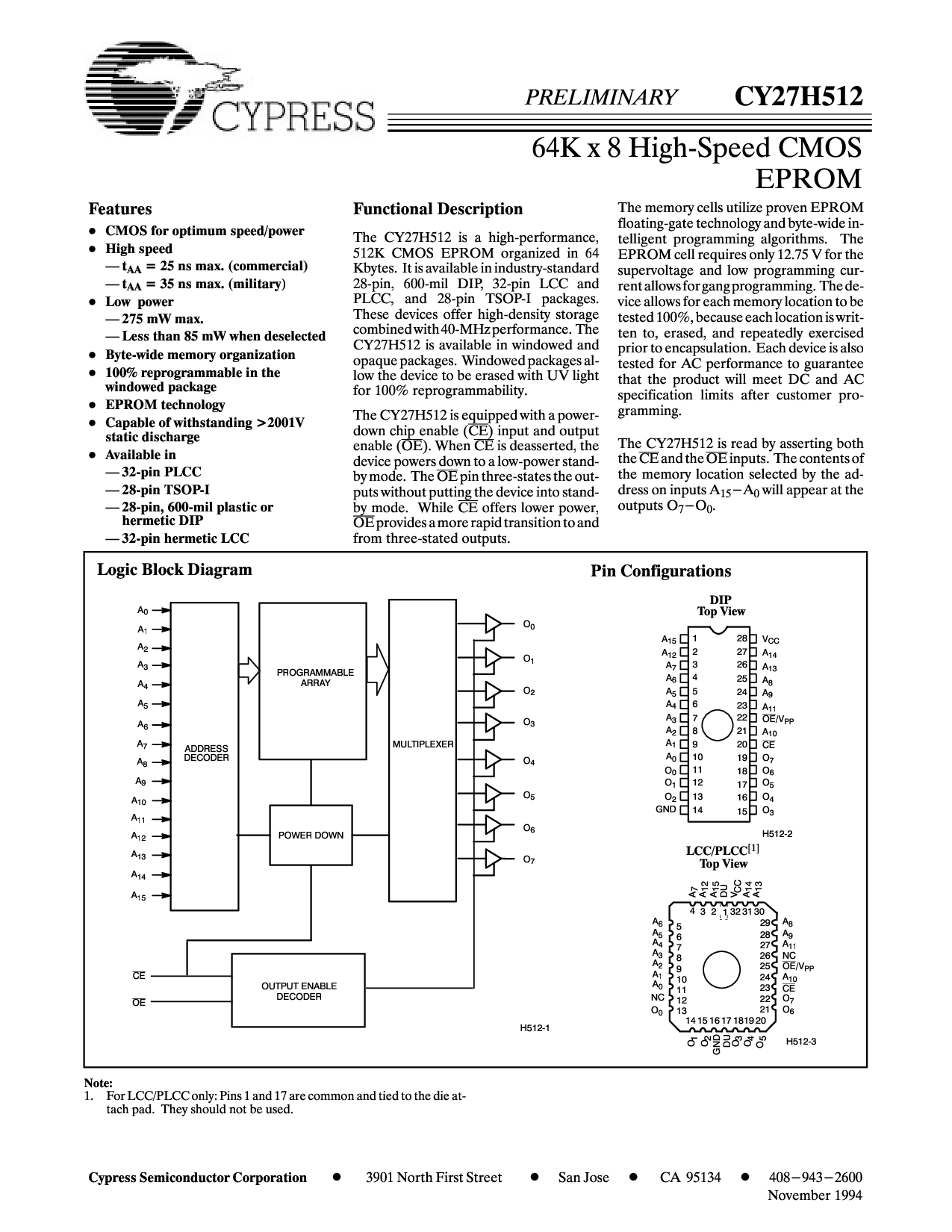

管脚 配置

特点

d

CMOS 用于 最佳 速度/电源

d

高 速度

Ċ

t

AA

= 25 ns 最大值 (商业)

Ċ

t

AA

= 35 ns 最大值 (军事)

d

低 电源

Ċ

275 mW 最大值

Ċ

较少 比 85 mW 当 取消选择

d

ByteĆwide 记忆 组织机构

d

100% 可重新编程 入点 这

窗口化 包装

d

非易失存储器 技术

d

有能力 的 承受 >2001v

静态 放电

d

可用 入点

Ċ

32Ćpin PLCC

Ċ

28Ćpin TSOPĆI

Ċ

28Ćpin, 600Ćmil 塑料 或

密封 倾角

Ċ

32Ćpin 密封 LCC

功能 描述

这 CY27H512 是 一个 highĆperformance,

512K CMOS 非易失存储器 有组织的 入点 64

千字节.它 是可用入点 industryĆstandard

28Ćpin, 600Ćmil 倾角, 32Ćpin LCC 和

plcc, 和 28Ćpin TSOPĆI 软件包.

这些 设备 报价 highĆdensity 存储

合并与40ĆMHz业绩.这

CY27H512 是 可用 入点 窗口化 和

不透明软件包.窗口化 软件包alĆ

低 这 设备 至 是 已擦除 与 UV 灯光

用于 100% 可重新编程性.

这 CY27H512 是 配备 与 一个 powerĆ

向下 芯片 启用 (ce) 输入 和 输出

启用 (oe). 当 ce 是 取消断言, 这

设备 权力 向下 至 一个 lowĆpower standĆ

由模式. 这 oe

管脚 threeĆstates 这outĆ

看跌期权 无 推杆 这 设备 进入 standĆ

由 模式. 同时 ce

优惠 下部 电源,

oe提供一个更多快速过渡至和

从 threeĆstated 产出.

这 记忆 细胞 利用 经过验证 非易失存储器

floatingĆgate 技术 和 byteĆwide因

telligent 编程 算法. 这

非易失存储器 细胞 需要 仅 12.75 v 用于 这

超电压 和 低 编程 curĆ

租金允许用于帮派编程.这deĆ

副 允许 用于 每个 记忆 位置 至 是

已测试100%,因为每个位置是writĆ

十 至, 已擦除, 和 反复 行使

之前 至 封装. 每个 设备 是 也

已测试 用于 交流电 业绩 至 保函

那 这 产品 将 满足 直流 和 交流电

规格 限制 之后 客户 proĆ

gramming.

这 CY27H512 是 阅读 由 断言 两者都有

这ce

和这oe输入.这内容的

这 记忆 位置 已选择 由 这 adĆ

连衣裙 开启 输入 一个

15

-一个

0

将 出现 在 这

产出 o

7

-o

0

.

顶部 查看

倾角

H512Ć1

H512Ć2

顶部 查看

H512Ć3

可编程

阵列

o

0

o

1

o

7

o

2

o

4

o

3

o

5

o

6

地址

解码器

一个

0

一个

1

一个

2

一个

3

一个

4

一个

5

一个

6

一个

8

一个

7

多路复用器

一个

9

一个

10

一个

11

一个

12

一个

13

一个

14

一个

15

输出 启用

解码器

ce

oe

电源 向下

1

2

3

4

5

6

7

8

9

10

11

12

16

17

18

19

20

24

23

22

21

13

14

25

28

27

26

一个

15

一个

12

一个

7

一个

6

一个

5

一个

4

一个

3

一个

2

一个

1

一个

0

o

0

o

1

o

2

地

v

抄送

一个

14

一个

13

一个

8

一个

9

一个

11

oe/v

pp

一个

10

ce

o

7

o

6

o

4

o

5

o

3

15

12

o

0

31

4

5

6

7

8

9

10

32

1

30

13

14 15 16 17

26

25

24

23

22

21

11

一个

7

v

抄送

一个

6

一个

5

一个

4

一个

3

一个

2

一个

1

一个

0

ce

一个

9

一个

11

nc

一个

10

o

7

o

6

o

5

地

一个

8

oe/v

pp

一个

12

o

4

o

2

o

1

1819 20

27

28

29

32

nc

o

3

一个

15

一个

14

一个

13

du

du

lcc/plcc

[1]