2.5v 或 3.3v, 200-mhz, 1:18 时钟 分布 缓冲区

CY29942

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07284 rev. *b 修订 12月 21, 2002

42

特点

• 200-mhz 时钟 支持

• 2.5v 或 3.3v 操作

• lvcmos/lvttl 时钟 输入

• lvcmos-/lvttl-兼容 输入

• 18 时钟 产出: 驱动器 向上 至 36 时钟 线条

• 200 ps 最大值 输出到输出 偏斜

• 输出 启用 控制

• 管脚 兼容 与 mpc942c

•

可用 入点 工业 和 商业

•

32-管脚 lqfp 包装

描述

这 cy29942 是 一个 低电压 200-mhz 时钟 分布 buff-

er 与 一个 lvcmos 或 lvttl 兼容 输入 时钟. 全部 其他

控制 输入 是 lvcmos/lvttl 兼容. 这 十八

产出 是 2.5v 或 3.3v lvcmos 或 lvttl 兼容 和

可以 驱动器 50

Ω

系列 或 平行 已终止 变速器 线条.

用于 系列 已终止 变速器 线条, 每个 输出 可以

驱动器 一个 或 两个 痕迹 给予 这 设备 一个 有效 扇出

的 1:36. 低 输出到输出 偏斜 制造 这 cy29942 一个

理想 时钟 分布 缓冲区 用于 嵌套 时钟 树木 入点 这 大多数

要求苛刻 的 同步 系统.

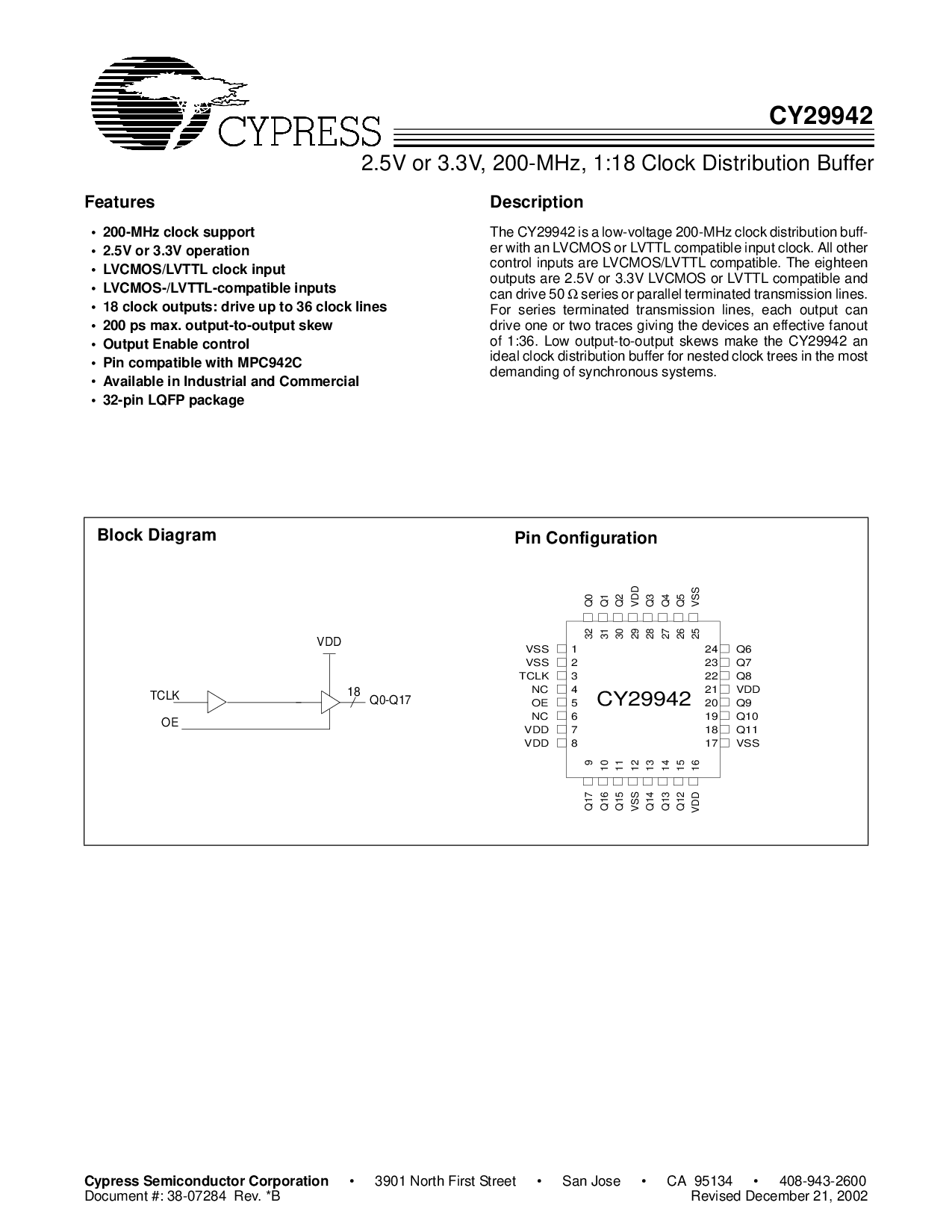

块 图表

管脚 配置

TCLK

oe

VDD

18

q0-q17

CY29942

Q0

Q1

Q2

VDD

Q3

Q4

Q5

vss

Q17

Q16

Q15

vss

Q14

Q13

Q12

VDD

Q6

Q7

Q8

VDD

Q9

Q10

Q11

vss

vss

vss

TCLK

nc

oe

nc

VDD

VDD

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25