72-mbit (2m x 36/4m x 18/1m x 72) 流水线

s

ync sram

CY7C1480V33

CY7C1482V33

CY7C1486V33

初步

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-05283 rev. *c 修订 12月 3, 2004

特点

• 支架 总线 操作 向上 至 250 mhz

• 可用 速度 等级 是 250, 200,167 mhz

• 已注册 输入 和 产出 用于 流水线 操作

• 3.3v 核心 电源 供应

• 2.5v / 3.3v 我/o 操作

• 快 时钟到输出 次

— 3.0 ns (用于 250-mhz 设备)

— 3.0 ns (用于 200-mhz 设备)

— 3.4 ns (用于 167-mhz 设备)

• 提供 高性能 3-1-1-1 访问权限 费率

•

用户可选择 突发 计数器 支撑 英特尔

®

Pentium

®

交错 或 线性 突发 序列

• 分开 处理器 和 控制器 地址 频闪

• 同步 自定时 写入

• 异步 输出 启用

• 单独 循环 芯片 取消选择

• cy7c1480v33 和 cy7c1482v33 提供 入点

电子元件工业联合会-标准 无铅 100-管脚 tqfp, 165-球 fbga

软件包. cy7c1486v33 可用 入点 209-球 bga

软件包

• ieee 1149.1 jtag-兼容 边界 扫描

• “zz” 睡眠 模式 选项

功能 描述

[1]

这 cy7c1480v33/cy7c1482v33/cy7c1486v33 sram

集成 2,097,152 x 36/4,194,304 x 18,1,048,576 × 72

sram 细胞 与 高级 同步 外围设备 电路

和 一个 两位 计数器 用于 内部 突发 操作. 全部

同步 输入 是 门控 由 寄存器 受控 由 一个

正-边缘-已触发 时钟 输入 (clk). 这 同步

输入 包括 全部 地址, 全部 数据 输入, 地址-流水线

芯片 启用 (ce

1

), 深度扩展 芯片 启用 (ce

2

和

ce

3

), 突发 控制 输入 (adsc, adsp, 和 adv), 写

启用 (bw

x

, 和 bwe), 和 全球 写 (gw).

异步 输入 包括 这 输出 启用 (oe

) 和 这

zz 管脚.

地址 和 芯片 启用 是 已注册 在 上升 边缘 的

时钟 当 要么 地址 频闪 处理器 (adsp

) 或

地址 频闪 控制器 (adsc

) 是 活动. 后续

突发 地址 可以 是 内部 已生成 作为 受控 由

这 预付款 管脚 (adv).

地址, 数据 输入, 和 写 一氧化碳ntrols 是 已注册 片上

至 启动 一个 自定时 写 cycle?.这个 零件 支架 字节 写

运营 (请参见 管脚 说明 和 真相 表 用于 进一步

详细信息). 写 循环次数 可以 是 一个至 两个 或 四 字节数 宽 作为

受控 由 这 字节 写 控制 输入. gw

当 活动

低

原因 全部 字节数 至 是 书面.

这 cy7c1480v33/cy7c1482v33/cy7c1486v33 操作

从 一个 +3.3v 核心 电源 供应 同时 全部 产出 将 操作

与 要么 一个 +2.5 或 +3.3v 供应. 全部 输入 和 产出 是

电子元件工业联合会-标准 jesd8-5-兼容.

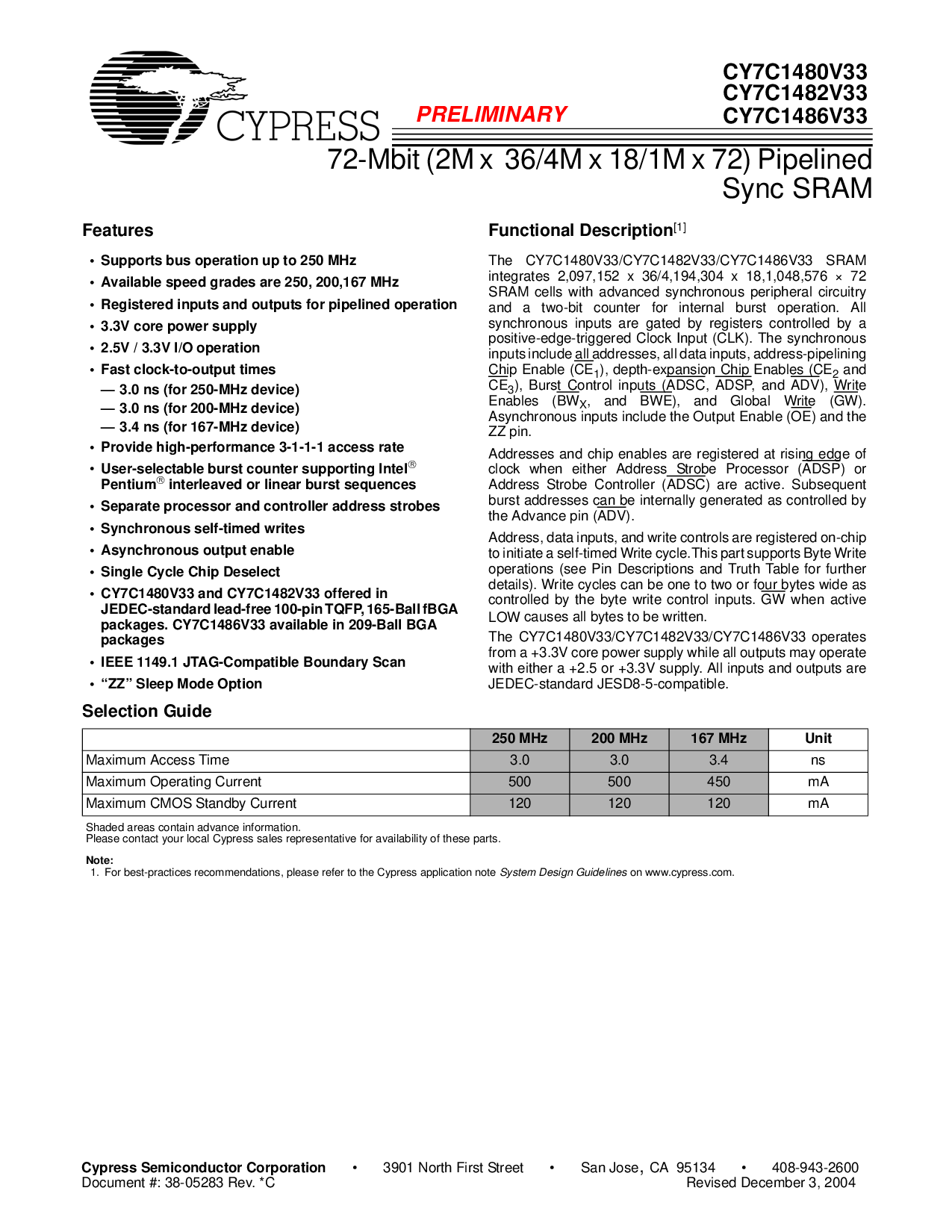

选择 指南

250 mhz 200 mhz 167 mhz 单位

最大值 访问权限 时间 3.0 3.0 3.4 ns

最大值 操作 电流

500 500 450 ma

最大值 cmos 备用 电流

120 120 120 ma

阴影 区域 包含 预付款 信息.

请 联系人 你的 本地 柏树 销售 代表 用于 可用性 的 这些 零件.

备注:

1. 用于 最佳实践 建议, 请 参考 至 这 柏树 应用程序 备注

系统 设计 准则

开启 www.柏树.com.