IS61SF12832

IS61SF12836

ISSI

®

综合 硅 解决方案, 公司 — 1-800-379-4774

1

rev. 一个

04/17/01

issi 储备金 这 右侧 至 制造 变更 至 其 产品 在 任何 时间 无 通知 入点 订单 至 改善 设计 和 供应 这 最好 可能 产品. 我们 假设 否 责任 用于 任何

错误 哪个 将 出现 入点 这个 出版物. © 版权 2001, 综合 硅 解决方案, 公司

特点

• 快 访问权限 次: 7.5 ns, 8 ns, 8.5 ns, 10 ns,

和 12 ns

• 内部 自定时 写 循环

• 个人 字节 写 控制 和 全球 写

• 时钟 受控, 已注册 地址, 数据

输入 和 控制 信号

• pentium™ 或 线性 突发 顺序 控制

使用 模式 输入

• 三个 芯片 启用 用于 简单 深度 扩展

和 地址 流水线

• 普通 数据 输入 和 数据 产出

• 电子元件工业联合会 100-管脚 tqfp 和

119-管脚 pbga 包装

• 单独 +3.3v +10%, –5% 电源 供应

• 掉电 贪睡 模式

描述

这

ISSI

is61sf12832 和 is61sf12836 是 高速

同步 静态 ram 设计 至 提供 一个 burstable,

高性能 记忆 用于 高 速度 联网 和

通信 应用程序. 它 是 有组织的 作为 131,072

字词 由 32 比特 或 36 比特, 预制 与

ISSI

's 高级

cmos 技术. 这 设备 集成 一个 2-有点 突发 计数器,

高速 sram 核心, 和 高驱动 能力 产出 进入

一个 单独 单片 电路. 全部 同步 输入 通过

通过 寄存器 受控 由 一个 正-边缘-已触发

单独 时钟 输入.

写 循环次数 是 内部 自定时 和 是 已启动 由 这

上升 边缘 的 这 时钟 输入. 写 循环次数 可以 是 从 一个 至

四 字节数 宽 作为 受控 由 这 写 控制 输入.

分开 字节 启用 允许 个人 字节数 至 是 书面.

BW1

控件 dqa,

BW2

控件 dqb,

BW3

控件 dqc,

BW4

控件 dqd, 条件 由

BWE

正在 低. 一个 低

开启

GW

输入 将 原因 全部 字节数 至 是 书面.

突发 可以 是 已启动 与 要么

ADSP

(地址 状态

处理器) 或

ADSC

(地址 状态 高速缓存 控制器) 输入

针脚. 后续 突发 地址 可以 是 已生成 内部

和 受控 由 这

adv

(突发 地址 预付款) 输入 管脚.

这 模式 管脚 是 已使用 至 选择 这 突发 顺序 订单,

线性 突发 是 已实现 当 这个 管脚 是 系紧 低. 交错

突发 是 已实现 当 这个 管脚 是 系紧 高 或 左 浮动.

128k x 32, 128k x 36 同步

流通 静态 ram

APRIL 2001

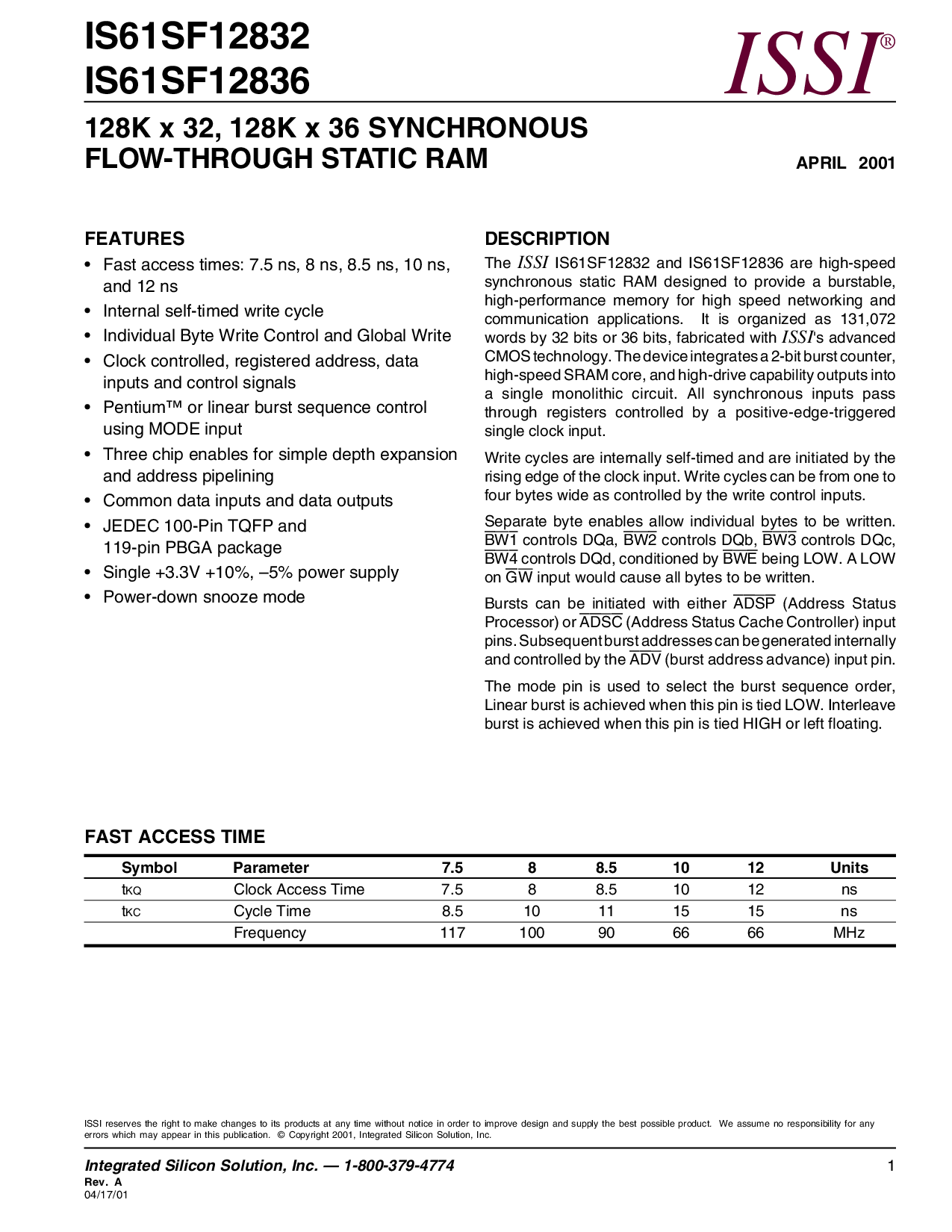

快 访问权限 时间

符号 参数 7.5 8 8.5 10 12 单位

t

KQ

时钟 访问权限 时间 7.5 8 8.5 10 12 ns

t

KC

循环 时间 8.5 10 11 15 15 ns

频率 117 100 90 66 66 MHz