© 2001 xilinx, 公司 全部 权利 保留. 全部 xilinx 商标, 已注册 商标, patents, 和 免责声明 是 作为 已列出 一个t

http://www.xilinx.com/法律.htm

.

全部 其他 商标 和 已注册 商标 是 这 适当的ty 的 他们的 各自 业主. 全部 规格 是 主题 至 change 无 通知.

ds003-1 (v2.5 ) april 2, 2001

www.xilinx.com

模块 1 的 4

产品 规格

1-800-255-7778 1

特点

• 快, 高密度 字段-可编程 闸门 阵列

- 密度 从 50k 至 1m 系统 盖茨

- 系统 业绩 向上 至 200 mhz

- 66-mhz pci 符合

- 热-可交换 用于 紧凑型 pci

• 多-标准 selectio™ 接口

- 16 高性能 接口 标准

- 连接 直接 至 zbtram 设备

• 内置 时钟-管理 电路

- 四 专用 延迟-已锁定 循环 (dlls) 用于

高级 时钟 控制

- 四 主要 低偏斜 全球 时钟 分布

nets, 加号 24 次要 本地 时钟 nets

• hierarchical 记忆 系统

- luts 可配置 作为 16-有点 ram, 32-有点 ram,

16-有点 双端口 ram, 或 16-有点 轮班 注册

- 可配置 同步 双端口 4k-有点

RAMs

- 快 接口 至 外部 高性能 rams

• 灵活 体系结构 那 余额 速度 和 密度

- 专用 进位 逻辑 用于 高速 算术

- 专用 乘数 支持

- 级联 链条 用于 宽输入 功能

- abundant 寄存器/锁扣 与 时钟 启用, 和

双 同步/异步 设置 和 重置

- 内部 3-州 bussing

- ieee 1149.1 边界扫描 逻辑

- 模具温度 传感器 二极管

• 支持 由 fpga foundation™ 和 alliance

发展 系统

- 完成 support 用于 统一 图书馆, relationally

已放置 宏, 和 设计 经理

- 宽 选择 的 pc 和 workstation platforms

• sram-基于 在系统内 配置

- 无限 re-可编程性

- 四 编程 模式

•0.22

m

m 5-图层 金属 流程

• 100% 工厂 已测试

描述

这 virtex fpga 家庭 交付 高-业绩,

高容量 可编程 逻辑 解决方案. 戏剧性

增加 入点 硅 效率 结果 从 优化 这 新建

体系结构 用于 地点-和-路线 效率 和 开采 一个

侵略性 5-图层-金属 0.22

m

m cmos 流程. 这些

预付款 制造 virtex fpgas 强大的 和 灵活 alterna-

语 至 面具-编程 闸门 阵列. 这 virtex 家庭

包括 这 九 成员 显示 入点助教ble? 1.

建筑物 开启 经验 获得 从 上一个 世代 的

fpgas, 这 virtex 家庭 表示 一个 revolutionary 步骤

前进 入点 可编程 逻辑 设计. 组合 一个 宽

品种 的 可编程 系统 特点, 一个 富有 层次结构 的

快, 灵活 互连 资源, 和 高级 流程

技术, 这 virtex 家庭 交付 一个 高速 和

高容量 可编程 逻辑 解决方案 那 增强

设计 灵活性 同时 减少 时间-至-市场.

0

virtex™ 2.5 v

字段 可编程 闸门 阵列

ds003-1 (v2.5 ) april 2, 2001

03

产品 规格

右

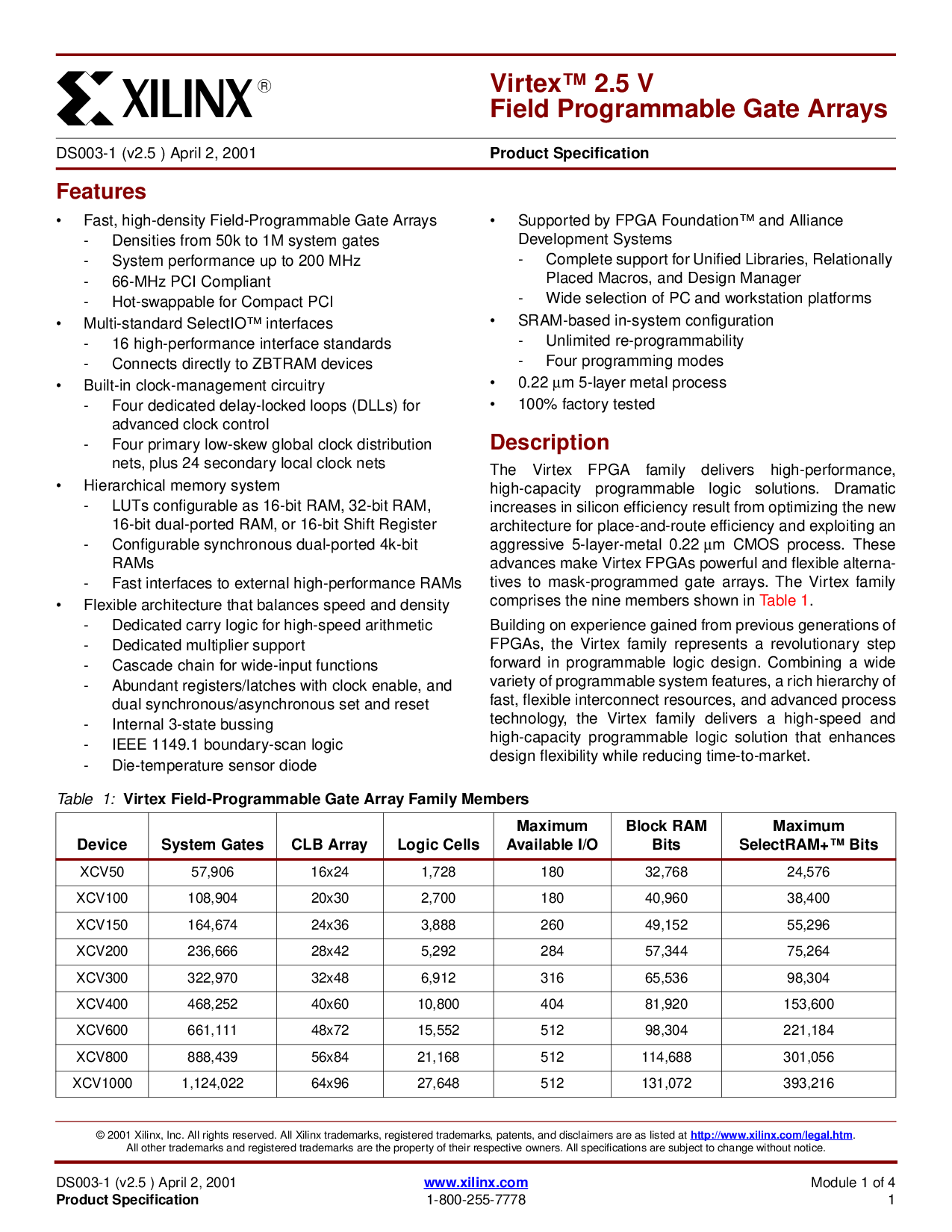

表 1:

virtex 字段-可编程 闸门 阵列 家庭 成员

设备 系统 盖茨 clb 阵列 逻辑 细胞

最大值

可用 我/o

块 ram

比特

最大值

SelectRAM+

™

比特

XCV50 57,906 16x24 1,728 180 32,768 24,576

XCV100 108,904 20x30 2,700 180 40,960 38,400

XCV150 164,674 24x36 3,888 260 49,152 55,296

XCV200 236,666 28x42 5,292 284 57,344 75,264

XCV300 322,970 32x48 6,912 316 65,536 98,304

XCV400 468,252 40x60 10,800 404 81,920 153,600

XCV600 661,111 48x72 15,552 512 98,304 221,184

XCV800 888,439 56x84 21,168 512 114,688 301,056

XCV1000 1,124,022 64x96 27,648 512 131,072 393,216