1

数据 工作表 获得 从 harris 半导体

SCHS165E

特点

• 异步 主人 重置

•j,

k, (d) 输入 至 第一 舞台

• 完全 同步 串行 或 平行 数据 转让

• 轮班 右侧 和 平行 荷载 能力

• 互补 输出 从 最后一个 舞台

• 缓冲 输入

• 典型 f

最大值

= 50mhz 在 v

抄送

= 5v,

c

l

= 15pf, t

一个

= 25

o

c

• 扇出 (结束 温度 范围)

- 标准 产出 . . . . . . . . . . . . . . . 10 lsttl 荷载

- 总线 驾驶员 产出 . . . . . . . . . . . . . 15 lsttl 荷载

• 宽 操作 温度 范围 . . . -55

o

c 至 125

o

c

• 平衡式 传播 延迟 和 过渡 次

• Signi 电源 减少 比较 至 lsttl

逻辑 ics

• hc 类型

- 2v 至 6v 操作

- 高 噪声 免疫: n

il

= 30%, n

ih

= 30%of v

抄送

在

v

抄送

= 5v

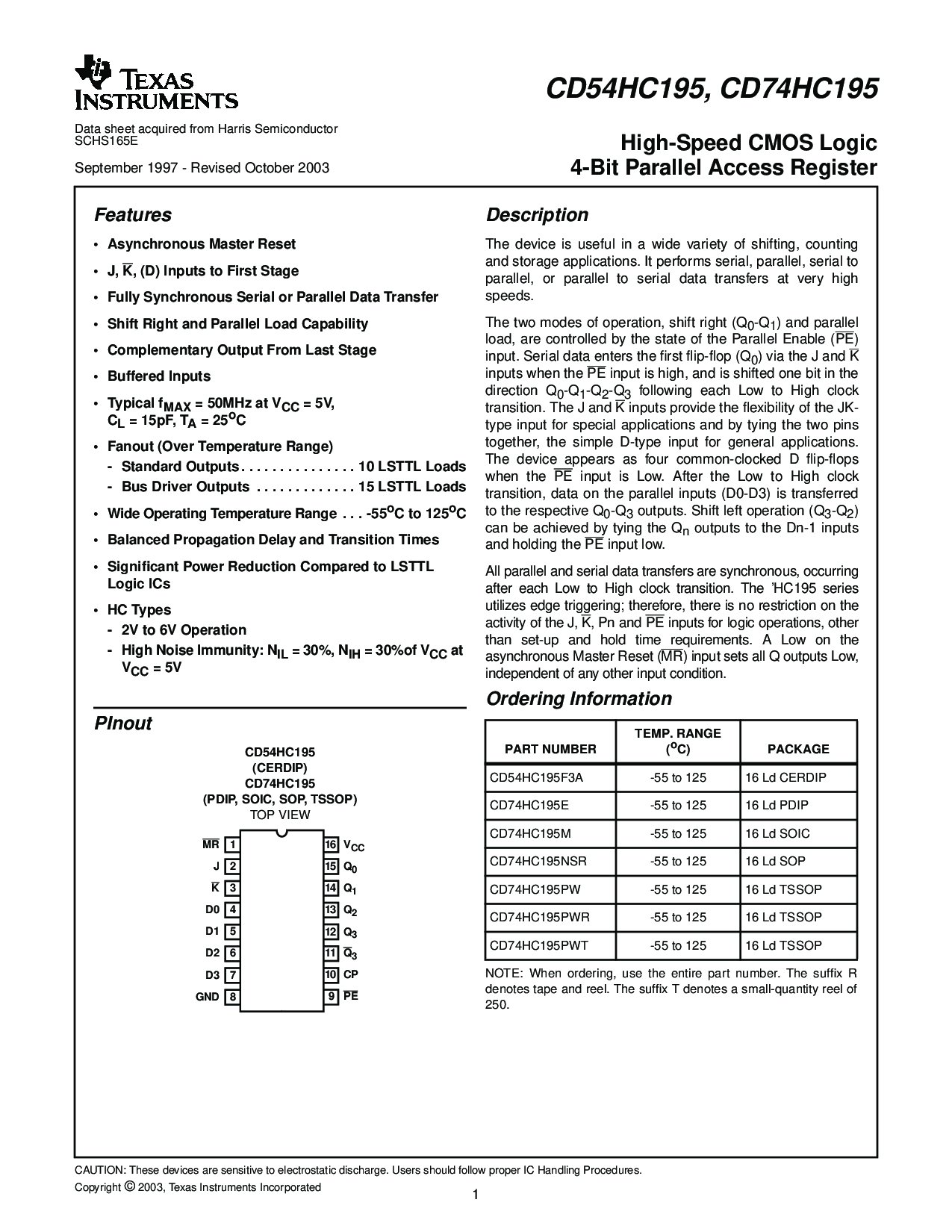

引出线

CD54HC195

(cerdip)

CD74HC195

(pdip, soic, sop, tssop)

顶部 查看

描述

这 设备 是 有用的 入点 一个 宽 品种 的 换档, 计数

和 存储 应用程序. 它 执行 串行, 平行, 串行 至

平行, 或 平行 至 串行 数据 转让 在 很 高

速度.

这 两个 模式 的 操作, 轮班 右侧 (q

0

-q

1

) 和 平行

荷载, 是 受控 由 这 州 的 这 平行 启用 (

pe)

输入. 串行 数据 进入 这 first flip-flop (q

0

) 通过 这 j 和 k

输入 当 这

pe 输入 是 高, 和 是 换档 一个 有点 入点 这

方向 q

0

-q

1

-q

2

-q

3

以下内容 每个 低 至 高 时钟

过渡. 这 j 和

k 输入 提供 这 fl 的 这 jk-

类型 输入 用于 特殊 应用程序 和 由 绑扎 这 两个 针脚

一起, 这 简单 d-类型 输入 用于 概述 应用程序.

这 设备 出现 作为 四 普通-时钟 d fl

当 这

pe 输入 是 低. 之后 这 低 至 高 时钟

过渡, 数据 开启 这 平行 输入 (d0-d3) 是 已转移

至 这 各自 q

0

-q

3

产出. 轮班 左 操作 (q

3

-q

2

)

可以 是 已实现 由 绑扎 这 q

n

产出 至 这 dn-1 输入

和 持有 这

pe 输入 低.

全部 平行 和 串行 数据 转让 是 同步, 正在发生

之后 每个 低 至 高 时钟 过渡. 这 ’HC195 系列

利用 边缘 触发; 因此, 那里 是 否 限制 开启 这

活动 的 这 j,

k, pn 和 pe 输入 用于 逻辑 运营, 其他

比 设置 和 保持 时间 要求. 一个 低 开启 这

异步 主人 重置 (

mr) 输入 集 全部 q 产出 低,

独立 的 任何 其他 输入 条件.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

MR

j

k

D0

D1

D2

地

D3

v

抄送

q

1

q

2

q

3

q

3

cp

pe

q

0

订购 信息

零件 号码

温度 范围

(

o

c) 包装

CD54HC195F3A -55 至 125 16 ld cerdip

CD74HC195E -55 至 125 16 ld pdip

CD74HC195M -55 至 125 16 ld soic

CD74HC195NSR -55 至 125 16 ld sop

CD74HC195PW -55 至 125 16 ld tssop

CD74HC195PWR -55 至 125 16 ld tssop

CD74HC195PWT -55 至 125 16 ld tssop

备注: 当 订购, 使用 这 整个 零件 号码. 这 suffix 右

表示 胶带 和 卷轴. 这 suffix t 表示 一个 小批量 卷轴 的

250.

九月 1997 - 修订 october 2003

注意事项: 这些 设备 是 敏感 至 静电 放电. 用户 应该 跟着 适当的 集成电路 搬运 程序.

版权

©

2003, 德州 仪器仪表 股份公司

cd54hc195, cd74hc195

高速 cmos 逻辑

4-有点 平行 访问权限 注册

[ /标题

(cd74

HC195

)

/

sub-

项目

(高

速度

CMOS

逻辑

4-有点

paral-

lel

访问权限

瑞吉斯-

之三)

/autho