1

cat93c46/56/57/66/86

1k/2k/2k/4k/16k-有点 microwire 串行 e?

2

舞会

特点

■

高 速度 操作:

– 93c46/56/57/66: 1mhz

– 93c86: 3mhz

■

低 电源 cmos 技术

■

1.8 至 6.0 电压 操作

■

可选择 x8 或 x16 记忆 组织机构

■

自定时 写 循环 与 自动清除

■

硬件 和 软件 写 保护

■

通电 inadvertant 写 保护

■

1,000,000 程序/擦除 循环次数

■

100 年份 数据 保留

■

商业, 工业 和 汽车

温度 范围

■

顺序 阅读 (除了 93c46)

■

程序 启用 (pe) 管脚 (93c86 仅)

93c46/56/57/66/86 f02

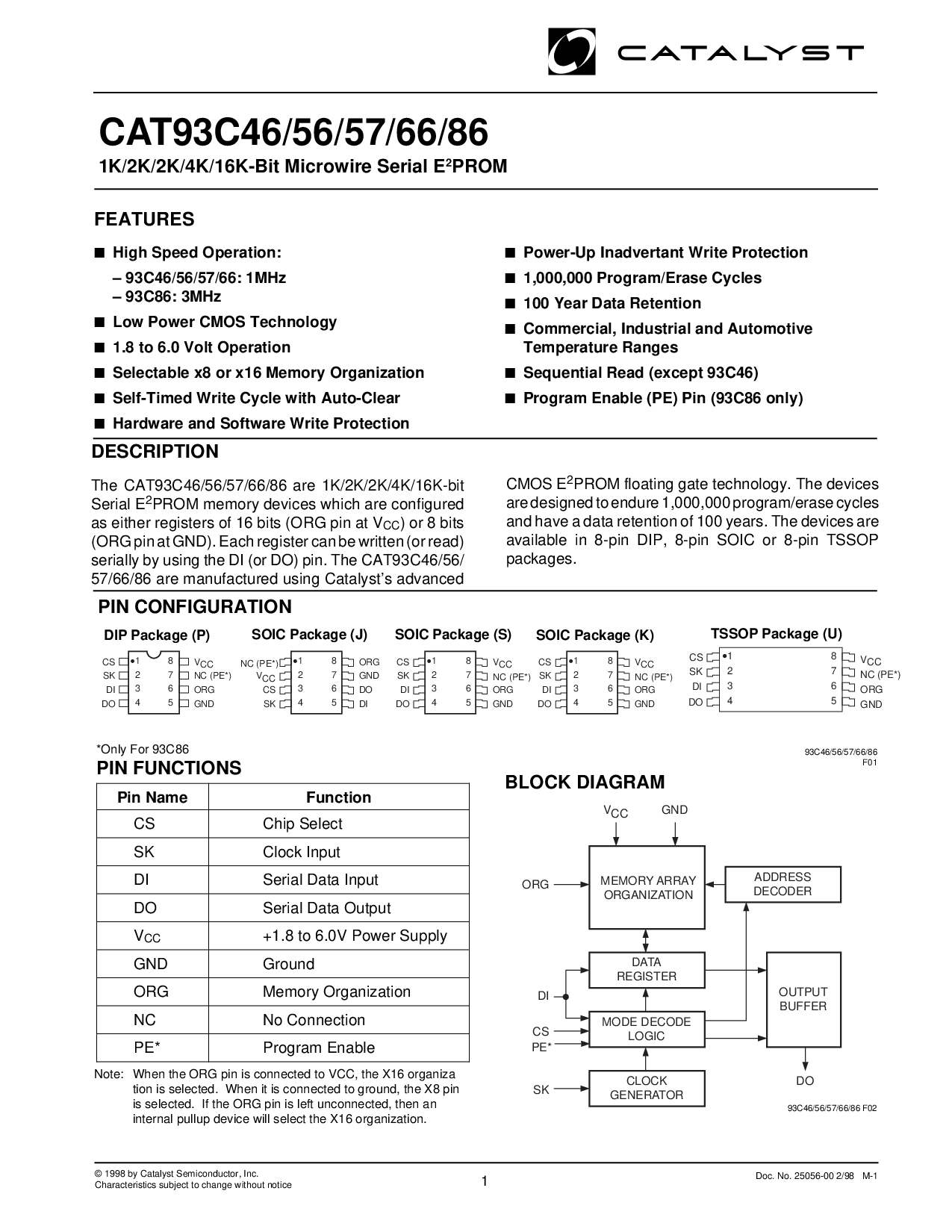

管脚 配置

倾角 包装 (p)

soic 包装 (j)

cmos e?

2

舞会 浮动 闸门 技术. 这 设备

是 设计 至 忍受 1,000,000 程序/擦除 循环次数

和 有 一个 数据 保留 的 100 年. 这 设备 是

可用 入点 8-管脚 倾角, 8-管脚 soic 或 8-管脚 tssop

软件包.

描述

这 cat93c46/56/57/66/86 是 1k/2k/2k/4k/16k-有点

串行 e?

2

舞会 记忆 设备 哪个 是 已配置

作为 要么 寄存器 的 16 比特 (org 管脚 在 v

抄送

) 或 8 比特

(org 管脚 在 地). 每个 注册 可以 是 书面 (或 阅读)

串行 由 使用 这 di (或 做) 管脚. 这 cat93c46/56/

57/66/86 是 已制造 使用 catalyst’s 高级

soic 包装 (s)

93c46/56/57/66/86

F01

管脚 功能

管脚 姓名 功能

cs 芯片 选择

sk 时钟 输入

di 串行 数据 输入

做 串行 数据 输出

v

抄送

+1.8 至 6.0v 电源 供应

地 接地

ORG 记忆 组织机构

nc 否 连接

PE* 程序 启用

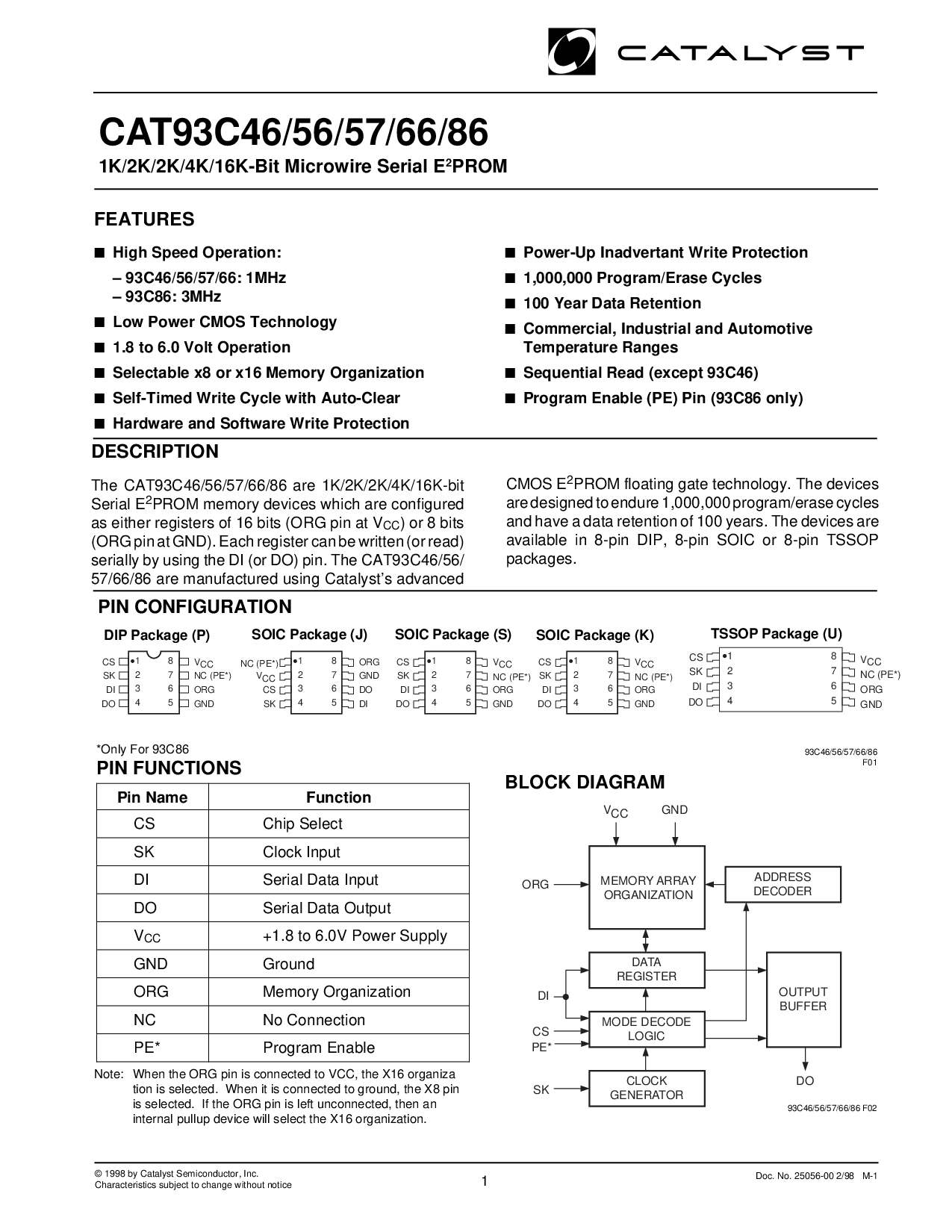

块 图表

备注: 当 这 org 管脚 是 已连接 至 vcc, 这 x16 organiza

操作 是 已选择. 当 它 是 已连接 至 接地, 这 x8 管脚

是 已选择. 如果 这 org 管脚 是 左 未连接, 然后 一个

内部 上拉 设备 将 选择 这 x16 组织机构.

soic 包装 (k)

© 1998 由 catalyst 半导体, 公司

特性 主题 至 变更 无 通知

tssop 包装 (u)

*only 用于 93c86

cs

sk

di

做

v

抄送

nc (pe*)

ORG

地

1

2

3

4

8

7

6

5

cs

sk

di

做

v

抄送

ORG

地

1

2

3

4

8

7

6

5

v

抄送

cs

sk

ORG

地

做

di

1

2

3

4

8

7

6

5

cs

sk

di

做

v

抄送

ORG

地

1

2

3

4

8

7

6

5

nc (pe*)

nc (pe*) nc (pe*)

8

7

6

5

v

抄送

ORG

地

di

cs

sk

做

1

2

3

4

nc (pe*)

v

抄送

地址

解码器

记忆 阵列

组织机构

数据

注册

模式 解码

逻辑

时钟

发电机

输出

缓冲区

做

sk

cs

di

ORG

地

PE*

doc. 否. 25056-00 2/98 m-1