ftg 用于 pentium 4

®

和 英特尔

®

845 系列 芯片et

CY28378

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07519 rev. ** 修订 二月 28,2003

特点

•C

ompatible 与 英特尔

®

ck-titan 和 ck-408 时钟

合成器/驾驶员 规格

• 系统 频率 合成器 用于 英特尔 brookdale 845

和 brookdale – g pentium 4

®

chipsets

• 可编程 时钟 输出 频率 与 较少 比

1-mhz 增量

• 综合 故障安全 看门狗 计时器 用于 系统

回收

• 自动 开关 至 hw 已选择 或 软件

编程 时钟 频率 当 看门狗 计时器

超时

• 可编程 3v66 和 pci 输出 频率 模式

• 有能力 的 生成 系统 重置 之后 一个 看门狗

计时器 超时 或 一个 变更 入点 输出 频率 通过

smbus 接口 发生

• 支持 smbus 字节 阅读/写 和 块 阅读/ 写

运营 至 简化 系统 bios 发展

• 供应商 id 和 修订 id 支持

• 可编程 驱动器 强度 支持

• 可编程 输出 偏斜 支持

• 电源 管理 控制 输入

• 可用 入点 48-管脚 ssop

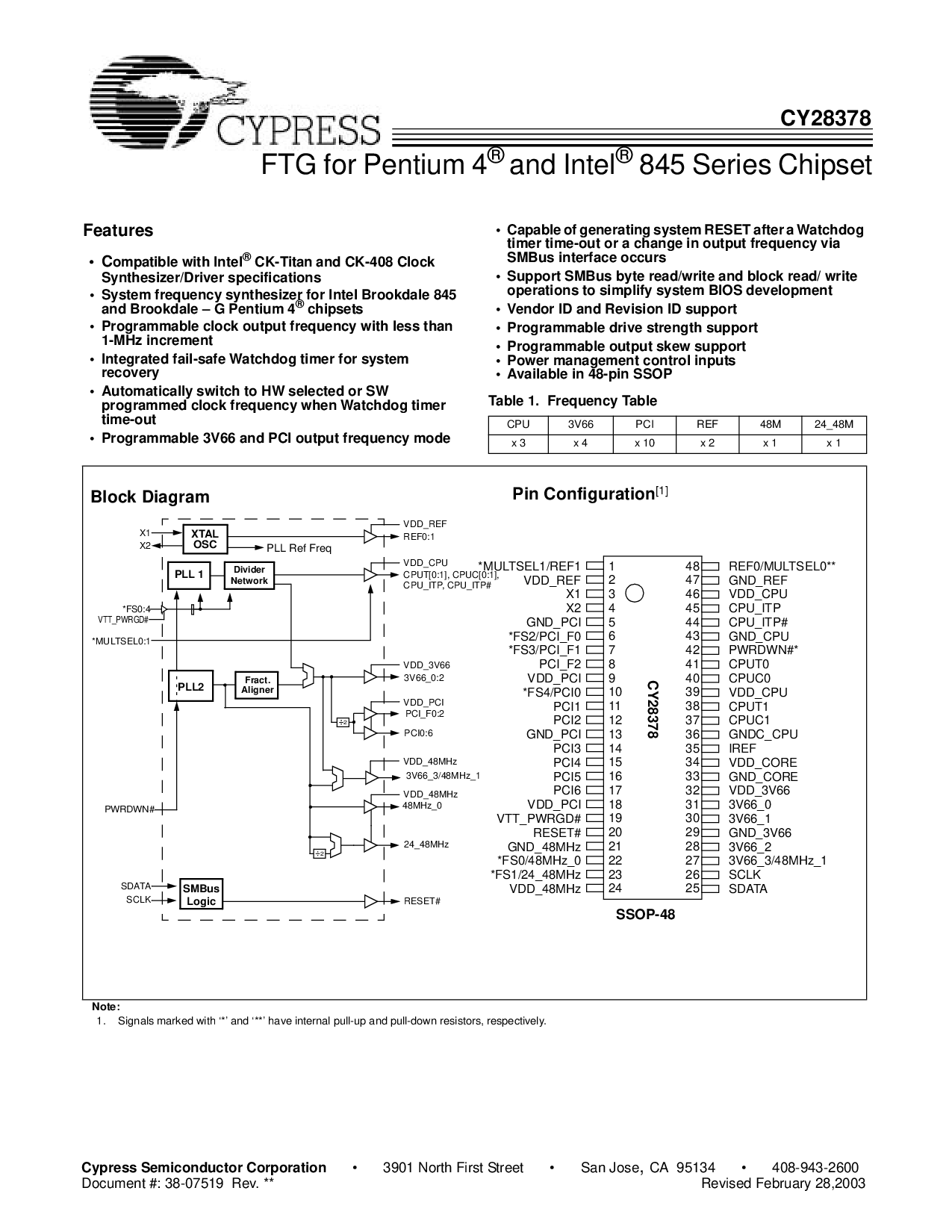

表 1. 频率 表

CPU 3V66 PCI 参考 48M 24_48m

x 3 x 4 x 10 x 2 x 1 x 1

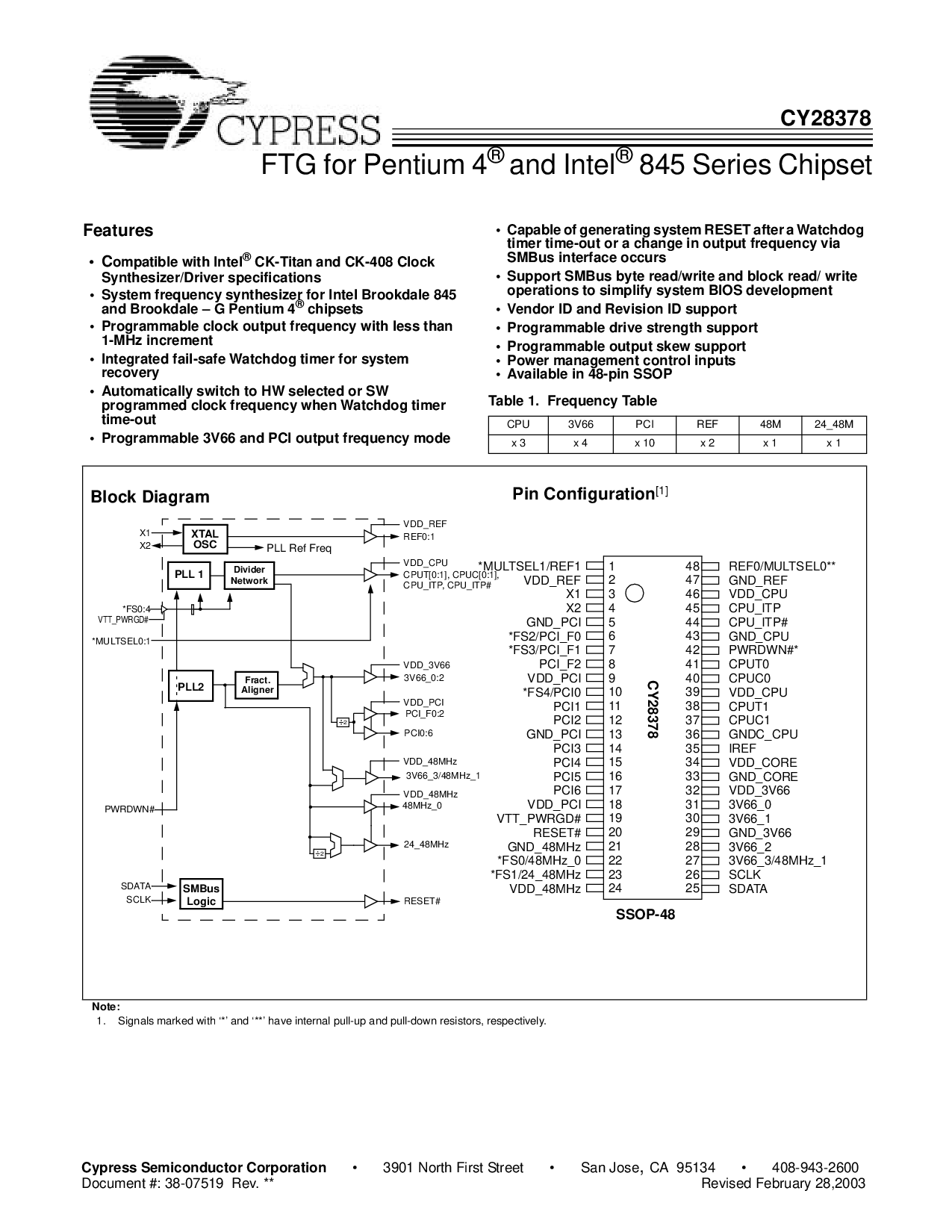

备注:

1. 信号 已标记 与 ‘*’ 和 ‘**’ 有 内部 上拉 和 下拉 电阻, 分别.

~

块 图表

vdd_参考

cput[0:1], cpuc[0:1],

XTAL

pll 参考 频率

X2

X1

vdd_pci

osc

SCLK

pll 1

SMBus

逻辑

vdd_48mhz

SDATA

vdd_3v66

分隔器

网络

vdd_cpu

*fs0:4

2

PWRDWN#

ssop-48

ref0:1

vtt_pwrgd#

*multsel1/ref1

vdd_参考

X1

X2

地_pci

*fs2/pci_f0

*fs3/pci_f1

pci_f2

vdd_pci

*fs4/pci0

PCI1

PCI2

地_pci

PCI3

PCI4

PCI5

PCI6

vdd_pci

vtt_pwrgd#

RESET#

地_48mhz

*fs0/48mhz_0

*fs1/24_48mhz

vdd_48mhz

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

28

27

26

25

32

31

30

29

ref0/multsel0**

地_参考

vdd_cpu

cpu_itp

cpu_itp#

地_cpu

PWRDWN#*

CPUT0

CPUC0

vdd_cpu

CPUT1

CPUC1

gndc_cpu

IREF

vdd_核心

地_核心

vdd_3v66

3v66_0

3v66_1

地_3v66

3v66_2

3v66_3/48mhz_1

SCLK

SDATA

CY28378

*multsel0:1

3v66_0:2

pci_f0:2

pci0:6

48mhz_0

24_48mhz

RESET#

cpu_itp, cpu_itp#

vdd_48mhz

3v66_3/48mhz_1

2

fract.

Aligner

PLL2

管脚 配置

[1]