ftg 用于 通过 pt880 串行 芯片组

CY28326

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07616 rev. *a 修订 六月 22, 2004

特点

• 支架 p4

CPUs

• 3.3v 电源 供应

• 十 副本 的 pci 时钟

• 一个 48 mhz usb 时钟

• 两个 副本 的 25 mhz 用于 src/局域网 时钟

• 一个 48 mhz/24 mhz 可编程 sio 时钟

• 三个 差速器 cpu 时钟 对

• smbus 支持 与 字节写/块 阅读/写

能力

• 传播 光谱 emi 减少

• 拨号盘-一个-频率

®

特点

• 自动 比率 特点

• 48-管脚 ssop 包装

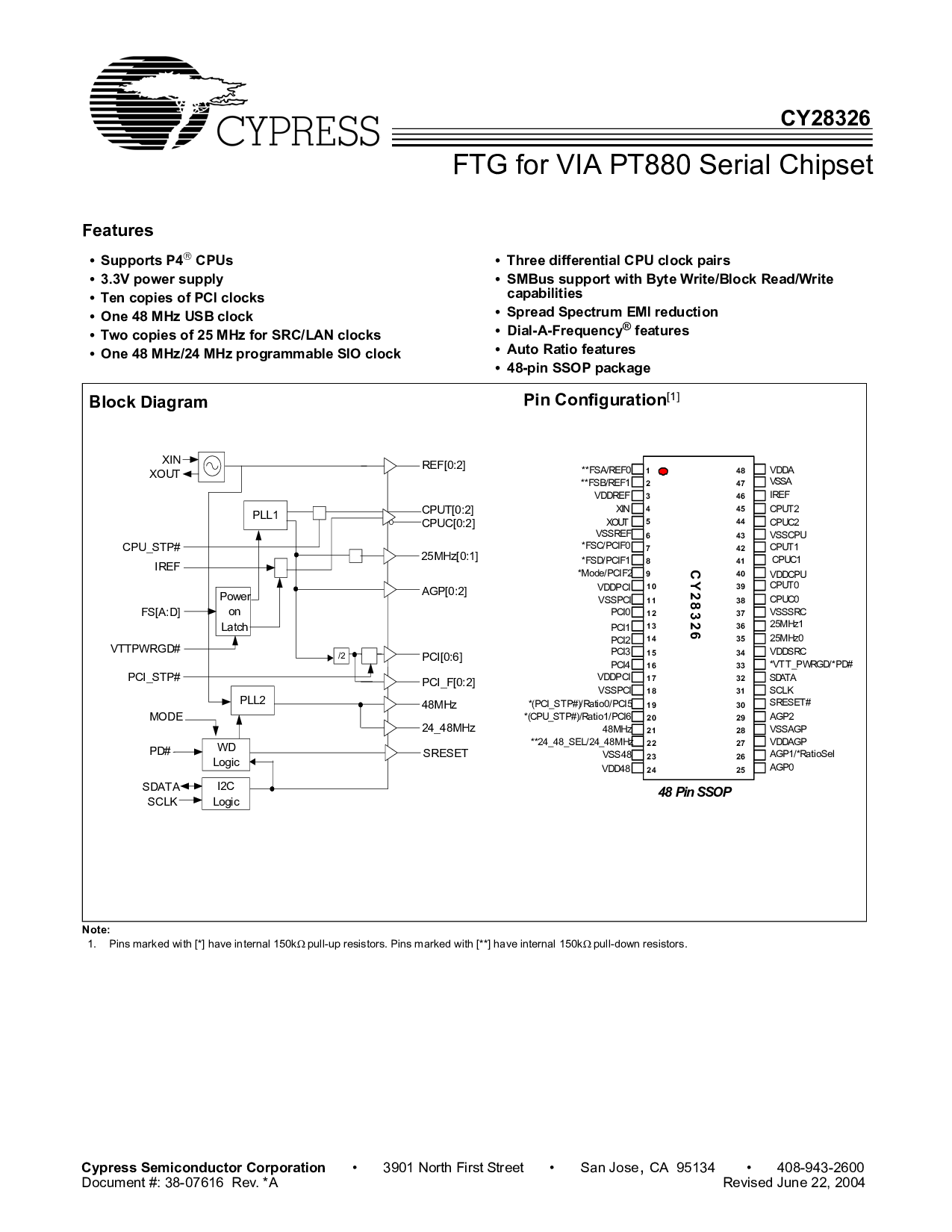

备注:

1. 针脚 已标记 与 [*] 有 内部 150k

Ω

上拉 电阻. 针脚 已标记 与 [**] 有 内部 150k

Ω

下拉 电阻.

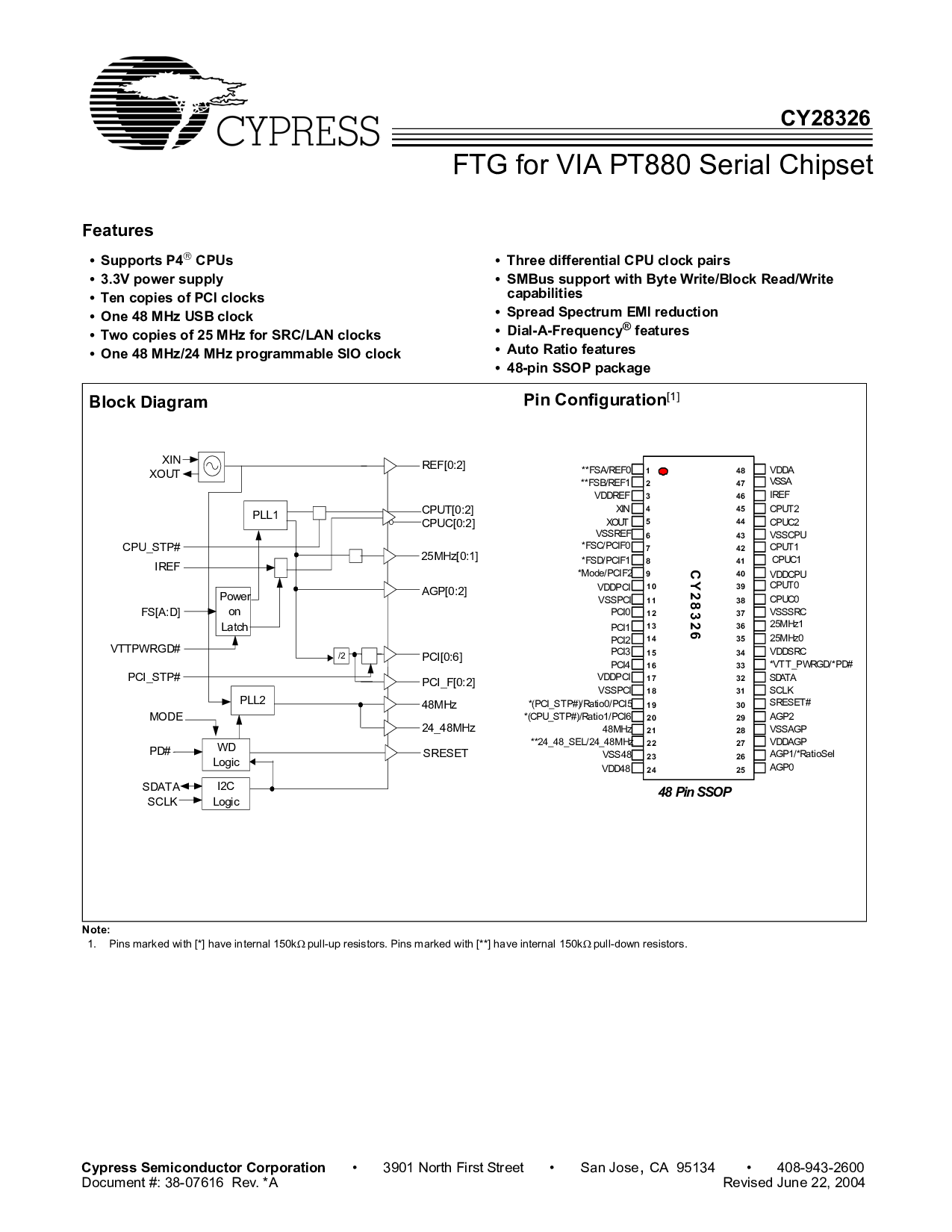

块 图表

管脚 配置

[1]

PLL1

PLL2

/2

WD

逻辑

新

XOUT

cpu_stp#

IREF

fs[a:d]

VTTPWRGD#

模式

PD#

SDATA

SCLK

24_48mhz

48MHz

pci_f[0:2]

pci[0:6]

agp[0:2]

ref[0:2]

I2C

逻辑

SRESET

电源

开启

门闩

cpuc[0:2]

cput[0:2]

25mhz[0:1]

pci_stp#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

VDDA

VSSA

IREF

CPUT2

CPUC2

VSSCPU

CPUT1

CPUC1

VDDCPU

CPUT0

CPUC0

VSSSRC

25MHz1

25MHz0

VDDSRC

*VTt_pwrgd/*PD#

SDATA

SCLK

SRESET#

AGP2

VSSAGP

VDDAGP

agp1/*ratioSel

AGP0

**fsa/ref0

**fsb/ref1

VDDREF

新

XOUT

VSSREF

*fsc/pcif0

*fsd/pcif1

*mode/pcif2

VDDPCI

VSSPCI

PCI0

PCI1

PCI2

PCI4

PCI3

VDDPCI

VSSPCI

*(pci_stp#)/比率o0/pci5

*(cpu_stP#)/右心房t我 o1/PCI6

48MHz

**24_48_选择/24_48mhz

VSS48

VDD48

CY28326

48 管脚 ssop