时钟 合成器 与 差速器 cpu 产出

CY28346

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07331 rev. *b 修订 12月 26, 2002

特点

• 符合 与 intel® ck 408 移动电话 时钟 合成器

规格

• 3.3v 电源 供应

• 三个 差速器 cpu 时钟

• 十 副本 的 pci 时钟

• 5/6 副本 的 3v66 时钟

• smbus 支持 与 回读 能力

• 传播 光谱 电磁 干扰 (emi)

减少

• 拨号盘-一个-frequency™ 特点

• 拨号盘-一个-db™ 特点

• 56-管脚 tssop 和 ssop 软件包

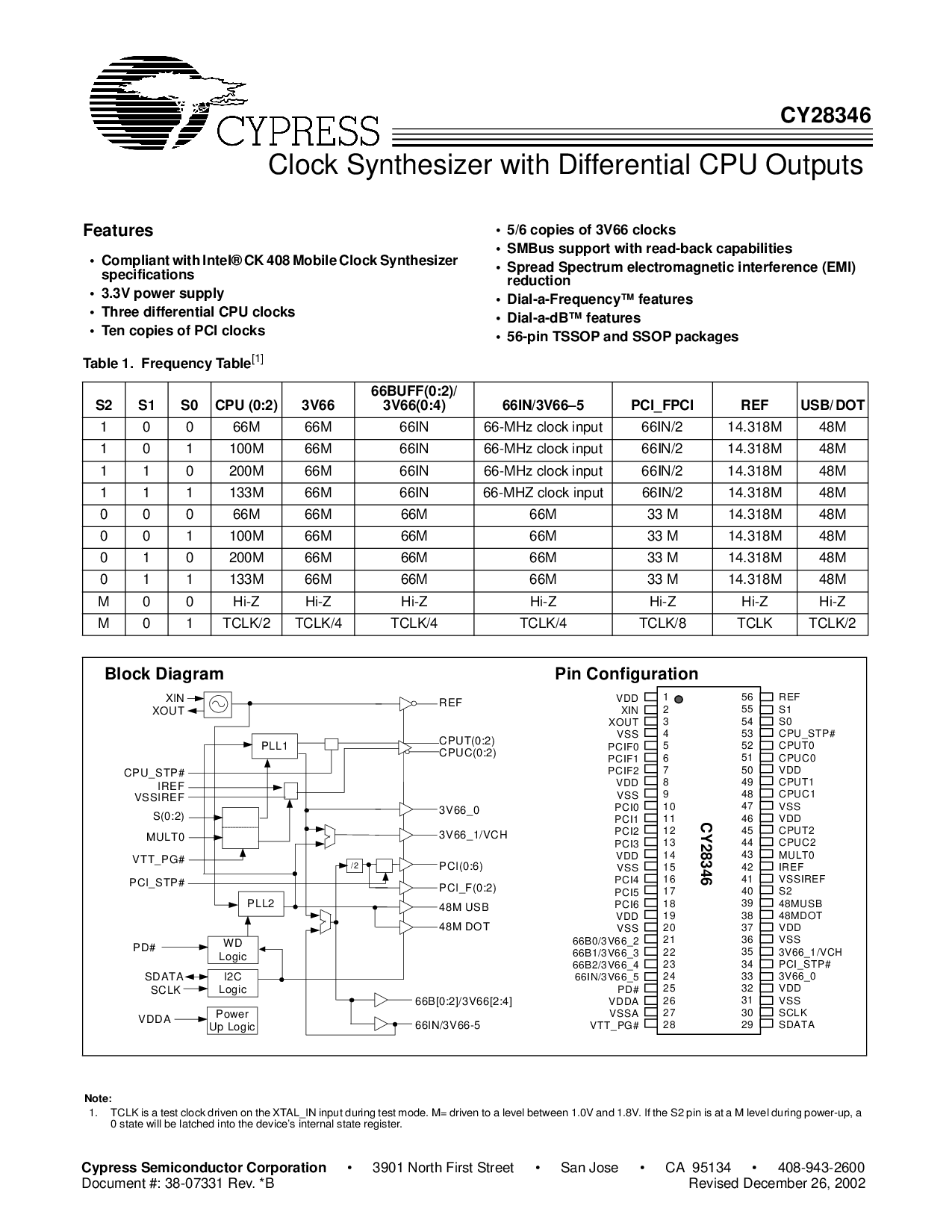

表 1. 频率 表

[1]

s2 s1 S0 cpu (0:2) 3V66

66buff(0:2)/

3v66(0:4) 66in/3v66–5 pci_fpci 参考 usb/ 圆点

1 0 0 66M 66M 66IN 66-mhz 时钟 输入 66in/2 14.318m 48M

1 0 1 100M 66M 66IN 66-mhz 时钟 输入 66in/2 14.318m 48M

1 1 0 200M 66M 66IN 66-mhz 时钟 输入 66in/2 14.318m 48M

1 1 1 133M 66M 66IN 66-mhz 时钟 输入 66in/2 14.318m 48M

0 0 0 66M 66M 66M 66M 33 m 14.318m 48M

0 0 1 100M 66M 66M 66M 33 m 14.318m 48M

0 1 0 200M 66M 66M 66M 33 m 14.318m 48M

0 1 1 133M 66M 66M 66M 33 m 14.318m 48M

m 0 0 嗨-z 嗨-z 嗨-z 嗨-z 嗨-z 嗨-z 嗨-z

m 0 1 tclk/2 tclk/4 tclk/4 tclk/4 tclk/8 TCLK tclk/2

备注:

1. tclk 是 一个 测试一下 时钟 驱动 开启 这 xtal_入点 输入 期间 测试一下 模式. m= 驱动 至 一个 水平 之间 1.0v 和 1.8v. 如果 这 s2 管脚是 在 一个 m 水平 期间 电源-向上, 一个

0 州 将 是 锁定 进入 这 设备

’

s 内部 州 注册.

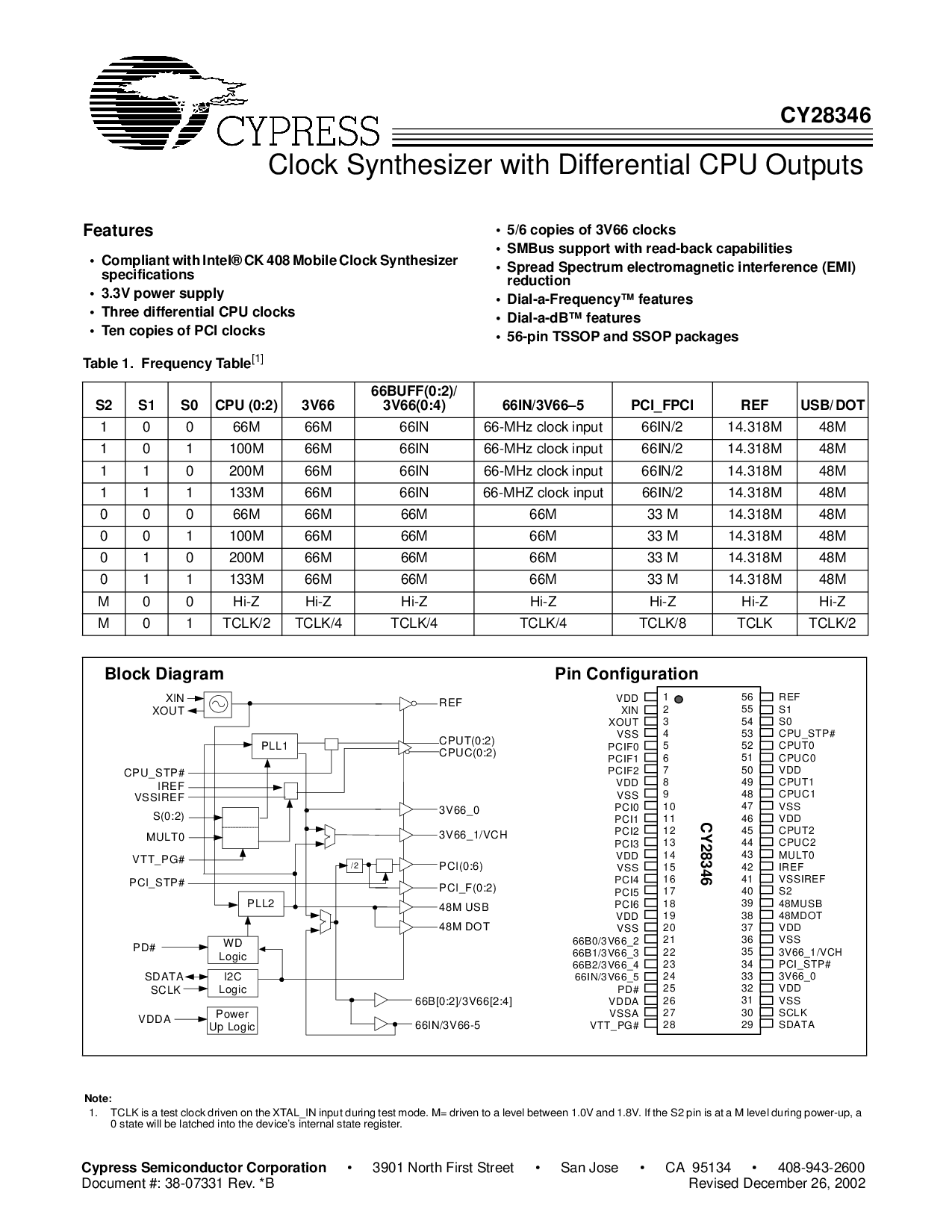

PLL1

PLL2

/2

WD

逻辑

电源

向上 逻辑

新

XOUT

cpu_stp#

IREF

VSSIREF

s(0:2)

MULT0

vtt_pg#

pci_stp#

PD#

SDATA

SCLK

VDDA

66b[0:2]/3v66[2:4]

48m 圆点

48m usb

pci_f(0:2)

pci(0:6)

3v66_1/vch

3v66_0

cpuc(0:2)

cput(0:2)

参考

66in/3v66-5

I2C

逻辑

VDD

新

XOUT

vss

PCIF0

PCIF1

PCIF2

VDD

vss

PCI0

PCI1

PCI2

PCI3

VDD

vss

PCI4

PCI5

PCI6

VDD

vss

66b0/3v66_2

66b1/3v66_3

66b2/3v66_4

66in/3v66_5

PD#

VDDA

VSSA

vtt_pg#

参考

S1

S0

cpu_stp#

CPUT0

CPUC0

VDD

CPUT1

CPUC1

vss

VDD

CPUT2

CPUC2

MULT0

IREF

VSSIREF

S2

48MUSB

48MDOT

VDD

vss

3v66_1/vch

pci_stp#

3v66_0

VDD

vss

SCLK

SDATA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

CY28346

管脚 配置块 图表