MediaClock™

mpeg 时钟 发电机 与 vcxo

CY24212

初步

柏树 半导体 公司

•

3901 北 第一 街道

•

San jose, ca 95134

•

408-943-2600

文件 #: 38-07402 rev. *b 修订 二月 18, 2003

特点 好处

• 综合 锁相 回路 (pll)

最高性能 pll 量身定制 用于 多媒体 应用程序

• 低 抖动, 高精度 产出

满足 关键 计时 要求 入点 复杂 系统 设计

• vcxo 与 模拟 调整

大型 ±150-ppm 范围, 更好 线性度

•

3.3v 操作

启用 应用程序 兼容性

零件 号码 产出 输入 频率 范围 输出 频率

cy24212-1 1 13.5 mhz/27 mhz (可选择) 27 mhz

cy24212-2 2 13.5 mhz/27 mhz (可选择) 两个 副本 的 27 mhz

cy24212-3 2 27 mhz 27 mhz/27.027 mhz (-1 ppm)

cy24212-5 2 27 mhz 27 mhz/27.027 mhz (0 ppm)

表 1. cy24212 (-1, -2) 频率 选择 选项

FSEL 参考 clka/clkb

0 13.5 mhz 27 mhz

1 27 mhz 27 mhz

表 2. cy24212 (-3, -5) 频率 选择 选项

FSEL 参考 CLKA CLKB

0 27 mhz 27 mhz 27 mhz

1 27 mhz 27 mhz 27.027 mhz

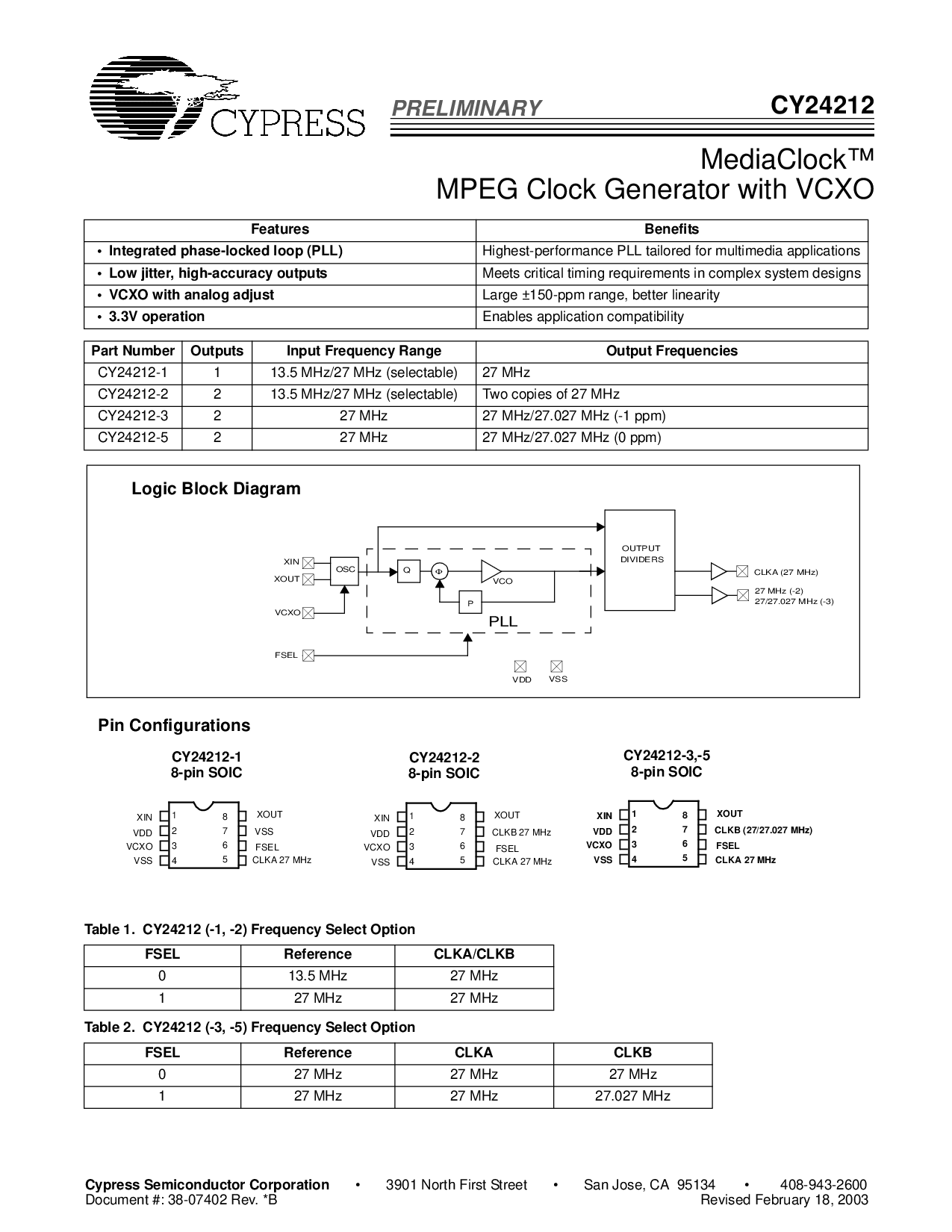

逻辑 块 图表

XOUT

输出

分隔器

PLL

osc

VCXO

q

p

VCO

VDD

vss

Φ

clka (27 mhz)

新

FSEL

27 mhz (-2)

27/27.027 mhz (-3)

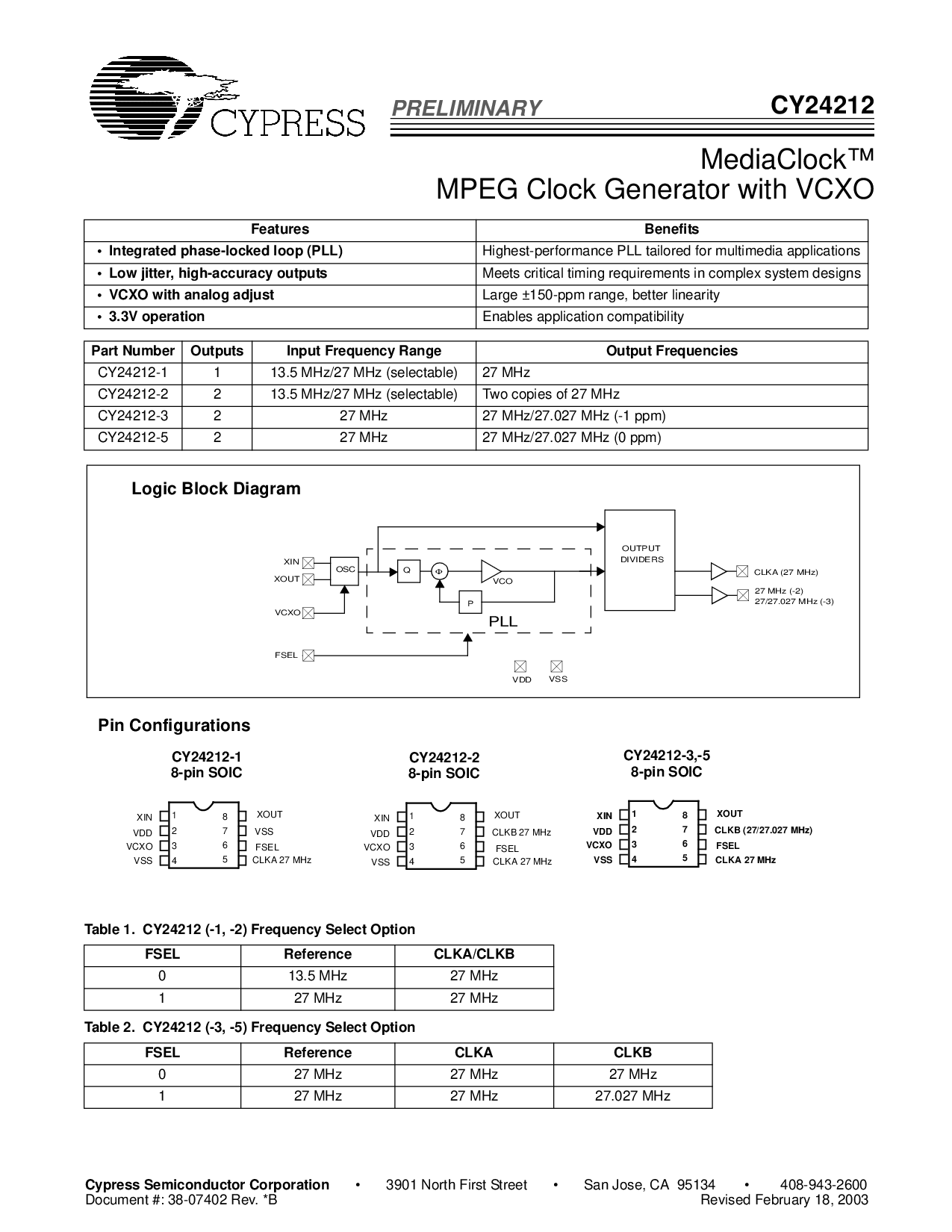

8-管脚 soic

cy24212-1

管脚 配置

1

2

3

4

XOUT

新

VCXO

clka 27 mhz

vss

vss

FSEL

5

6

7

8

VDD

8-管脚 soic

cy24212-2

1

2

3

4

XOUT

新

VCXO

clka 27 mhz

vss

clkb 27 mhz

FSEL

5

6

7

8

VDD

8-管脚 soic

cy24212-3,-5

1

2

3

4

XOUT

新

VCXO

clka 27 mhzvss

clkb (27/27.027 mhz)

FSEL

5

6

7

8

VDD