时钟 发电机 用于 ati

rs400 芯片组

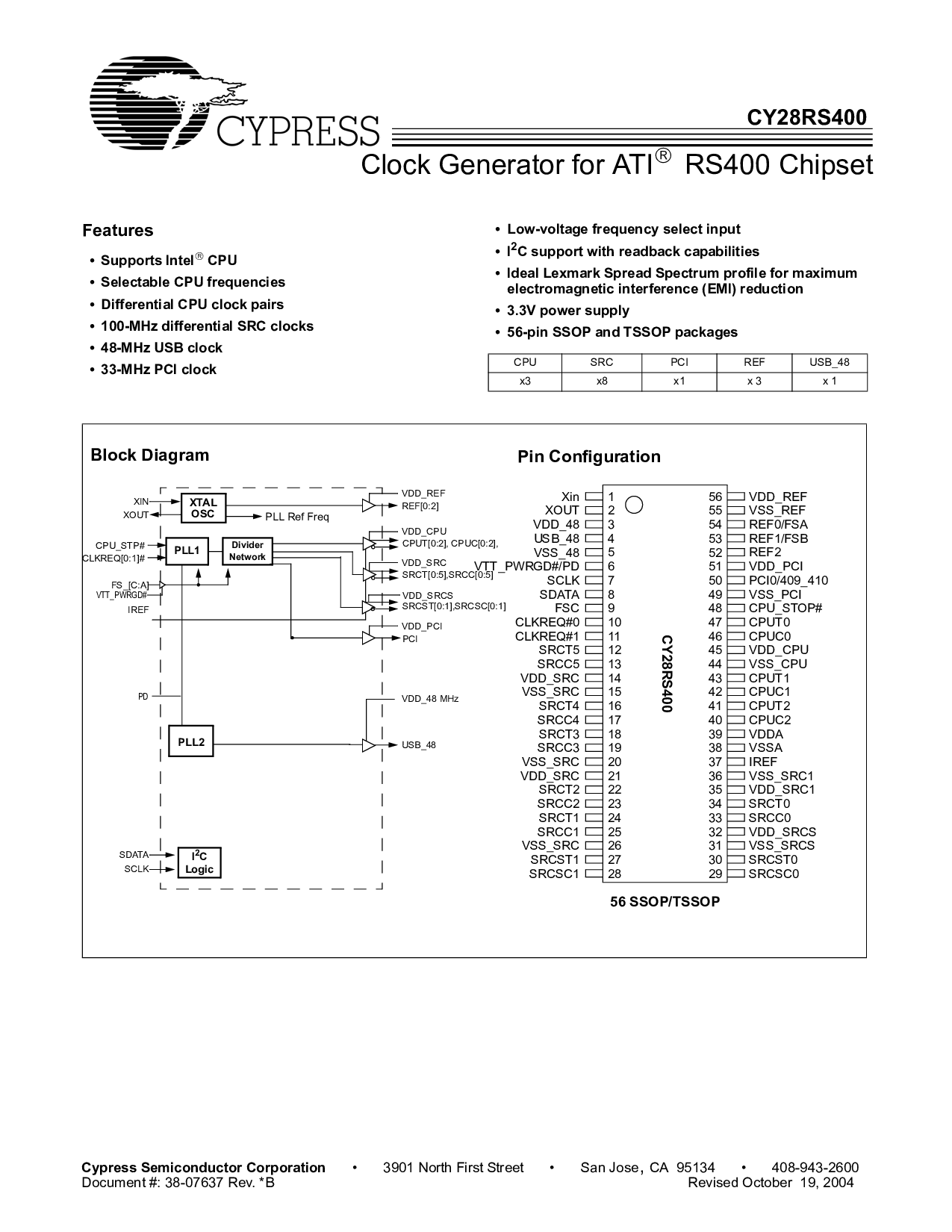

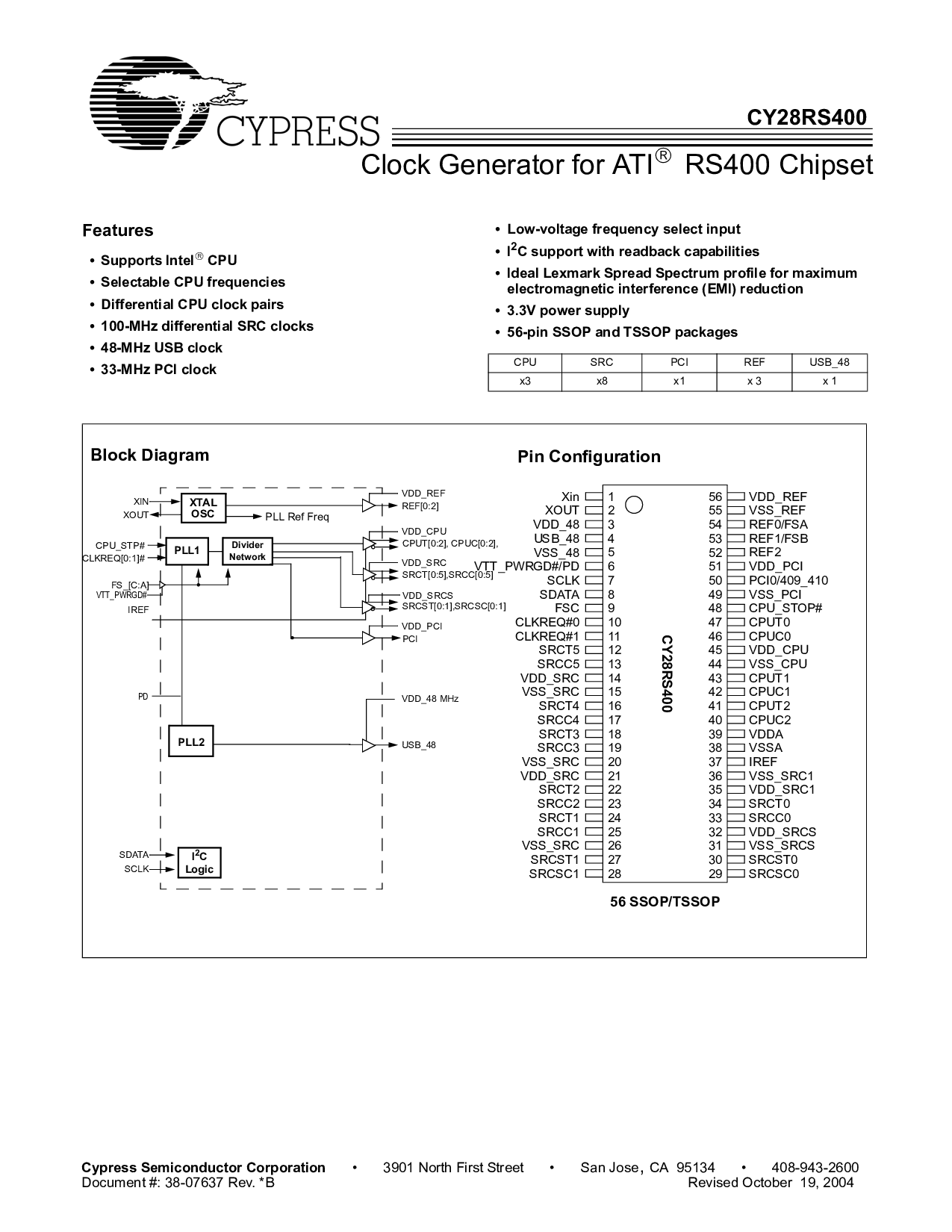

CY28RS400

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07637 rev. *b 修订 october 19, 2004

特点

• 支架 英特尔

CPU

• 可选择 cpu 频率

• 差速器 cpu 时钟 对

• 100-mhz 差速器 src 时钟

• 48-mhz usb 时钟

• 33-mhz pci 时钟

• 低电压 频率 选择 输入

•I

2

c 支持 与 回读 能力

• 理想 lexmark 传播 光谱 配置文件 用于 最大值

电磁 干扰 (emi) 减少

• 3.3v 电源 供应

• 56-管脚 ssop 和 tssop 软件包

CPU src PCI 参考 usb_48

x3 x8 x1 x 3 x 1

块 图表

管脚 配置

新

XOUT

usb_48

vss_48

vtt_pwrgd#/pd

SCLK

SDATA

FSC

CLKREQ#0

CLKREQ#1

SRCT5

SRCC5

vdd_src

vss_src

SRCT4

SRCC4

SRCT3

SRCC3

vss_src

vdd_src

SRCT2

SRCC2

SRCT1

SRCC1

vdd_参考

vss_参考

SRCST0

vss_src1

VSSA

IREF

VDDA

CPUT2

CPUC2

CPUC1

vss_cpu

CPUT1

vdd_cpu

CPUT0

CPUC0

cpu_stop#

pci0/409_410

vdd_pci

ref1/fsb

REF2

ref0/fsa

vdd_src1

vss_src

SRCST1

SRCSC1

SRCT0

SRCC0

vss_srcs

SRCSC0

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

32

31

30

29

vdd_参考

XTAL

pll 参考 频率

XOUT

新

osc

SCLK

PLL1

我

2

c

逻辑

vdd_48 mhz

SDATA

vdd_pci

分隔器

网络

vdd_cpu

fs_[c:a]

ref[0:2]

vtt_pwrgd#

IREF

PCI

PLL2

cput[0:2], cpuc[0:2],

vdd_src

srct[0:5],srcc[0:5]

usb_48

cpu_stp#

clkreq[0:1]#

vdd_48

vdd_srcs

vss_pci

CY28RS400

56 ssop/tssop

pd

vdd_srcs

srcst[0:1],srcsc[0:1]