failsafe™ 2.5v/ 3.3v 零 延迟 布菲右

CY23FS04

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07304 rev. *b 修订 october 12, 2004

特点

• 内部 dcxo 用于 连续 无故障 操作

• 零 输入-输出 传播 延迟

• 低抖动 (&指示灯; 35 ps rms) 产出

• 低 输出到输出 偏斜 (&指示灯; 200 ps)

• 4.17 mhz–170 mhz 参考 输入

• 支架 行业 标准 输入 晶体

•170 mhz 产出

• 5v-宽容 输入

• 锁相 回路 (pll) 旁路 模式

• 双 参考 输入

• 16-管脚 tssop

• 2.5v 或 3.3v 输出 电源 供应品

• 3.3v 核心 电源 供应

• 工业 温度 可用

功能 描述

这 cy23fs04 是 一个 failsafe

零 延迟 缓冲区 与 两个

参考 时钟 输入 和 四 相位-对齐 产出. 这

设备 提供 一个 最佳 解决方案 用于 应用程序 在哪里

连续 操作 是 必填项入点 这 事件 的 一个 主要 时钟

故障.

这 连续, 无故障 操作 是 已实现 由 使用 一个

dcxo, 哪个 服务 作为 一个 冗余 时钟 来源 入点 这 事件

的 一个 参考 时钟 故障 由 维护 这 最后一个 频率

和 相位 信息 的 这 参考 时钟.

这 独一无二 功能 的 这 cy23fs04 是 那 这 dcxo 是 入点

事实 这 主要 时钟 s来源, 哪个 是 已同步

(相位-对齐) 至 这 外部 参考 时钟. 当 这个

外部 时钟 是 已恢复, 这 dcxo 自动 resynchro-

N化 至 这 外部 时钟.

这 频率 的 这 水晶, 哪个 将 是 已连接 至 这

dcxo 必须 是 已选择 至 是 一个整数 因素 的 这 频率

的 这 参考 时钟. 这个 因素 是 设置 由 两个 选择 线条:

s[2:1], 请 请参见

助教ble? 1

. 输出 电源 供应, vdd 可以 是

已连接 至 要么 2.5v 或3.3v. vddc 是 这 电源 供应

管脚 用于 内部 电路 和 必须 是 已连接 至 3.3v.

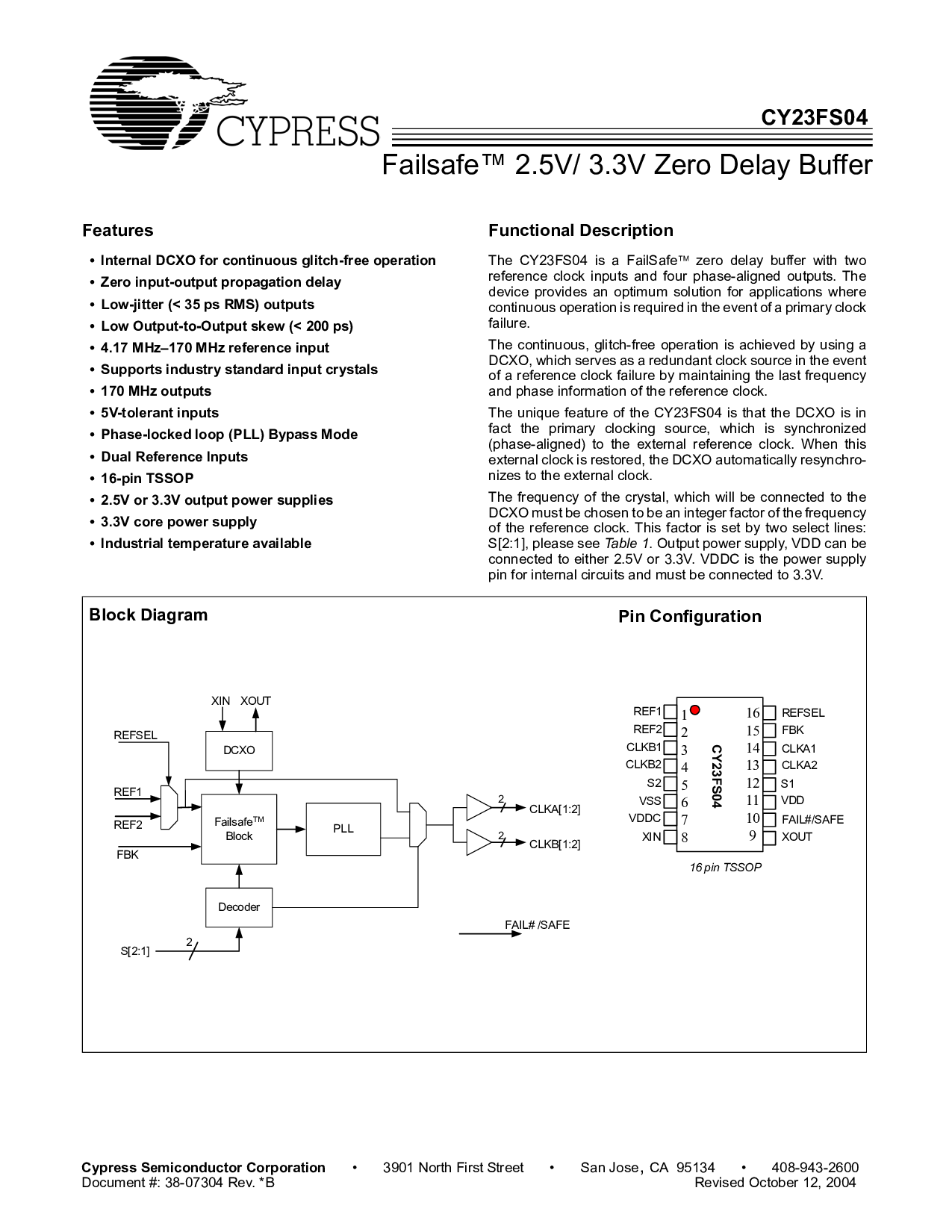

块 图表

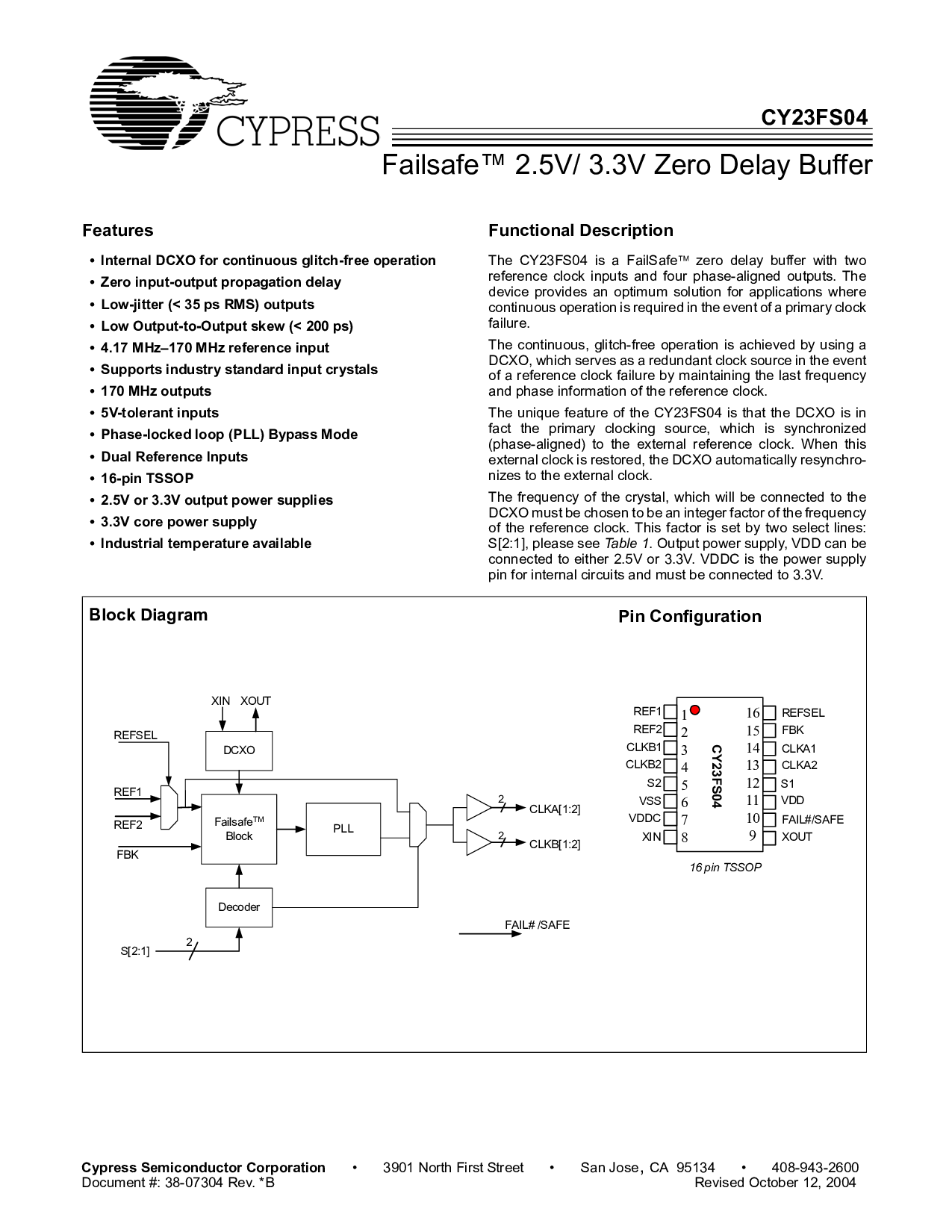

管脚 配置

clka[1:2]

clkb[1:2]

DCXO

解码器

2

Failsafe

tm

块

PLL

新 XOUT

2

2

REF2

FBK

s[2:1]

fail# /安全

REF1

REFSEL

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

CY23FS04

16 管脚 tssop

REF1

REF2

CLKB1

CLKB2

vss

VDDC

新

S2

REFSEL

FBK

CLKA1

CLKA2

S1

VDD

fail#/安全

XOUT