零 延迟 sdr/ddr 时钟 缓冲区

CY28343

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07369 rev. *a 修订 12月 26, 2002

特点

• 锁相 回路 时钟 分布 用于 ddr 和 sdr

sdram 应用程序

• 一个-单独-结束 时钟 输入 至 6 对 ddr 产出 或

13 sdr 产出.

• 外部 反馈 针脚 fbin_sdr/fbout_sdr 是

已使用 至 同步 这 产出 至 这 时钟 输入 用于

sdr.

• 外部 反馈 针脚 fbin_sdr/fbout_sdr 是

已使用 至 同步 这 产出 至 这 时钟 输入 用于

ddr.

• smbus 接口 启用/禁用 产出.

• 符合 至 电子元件工业联合会 sdr/ddr 规格

• 低 抖动, 低 偏斜

• 48 管脚 ssop 包装

备注:

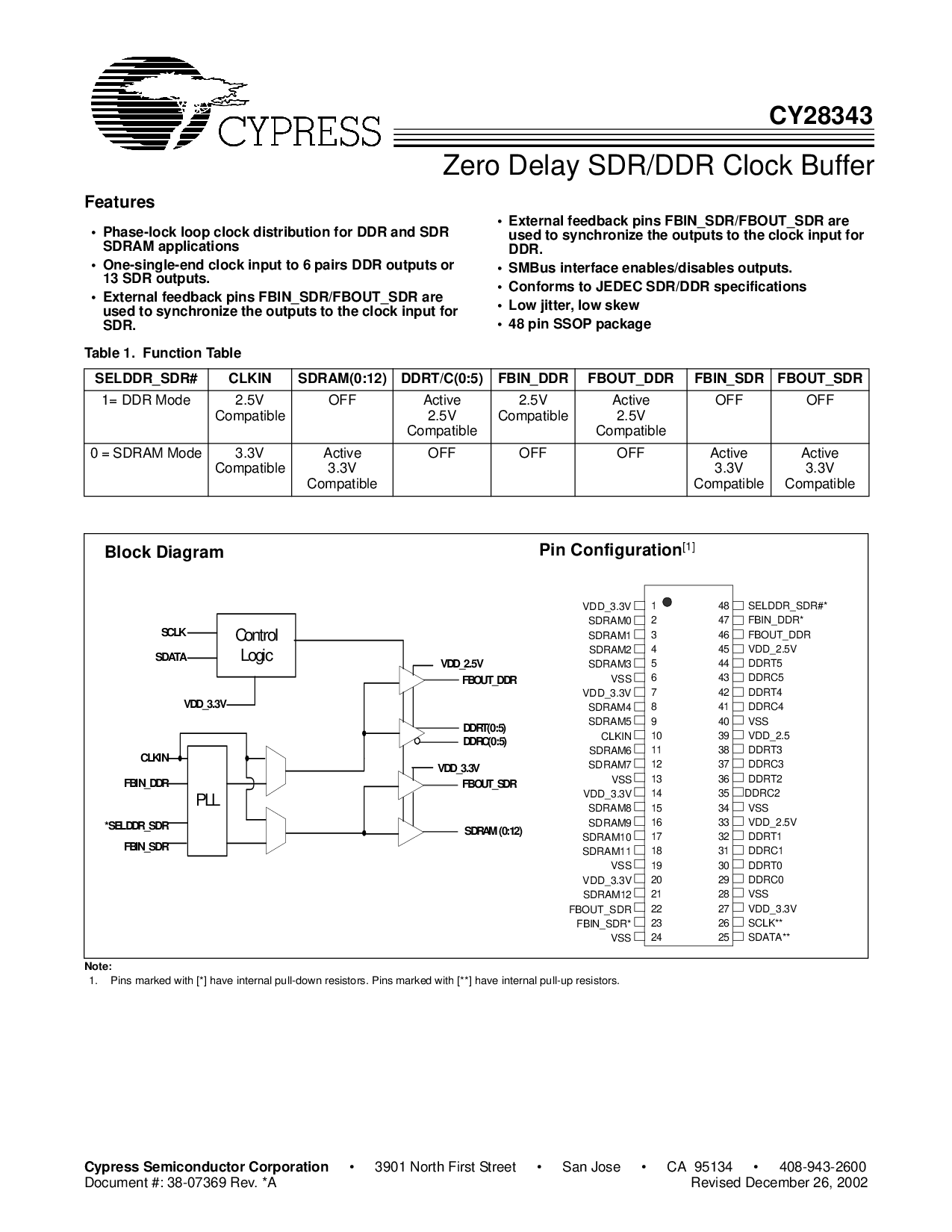

1. 针脚 已标记 与 [*] 有 内部 下拉 电阻. 针脚 已标记 与 [**] 有 内部 上拉 电阻.

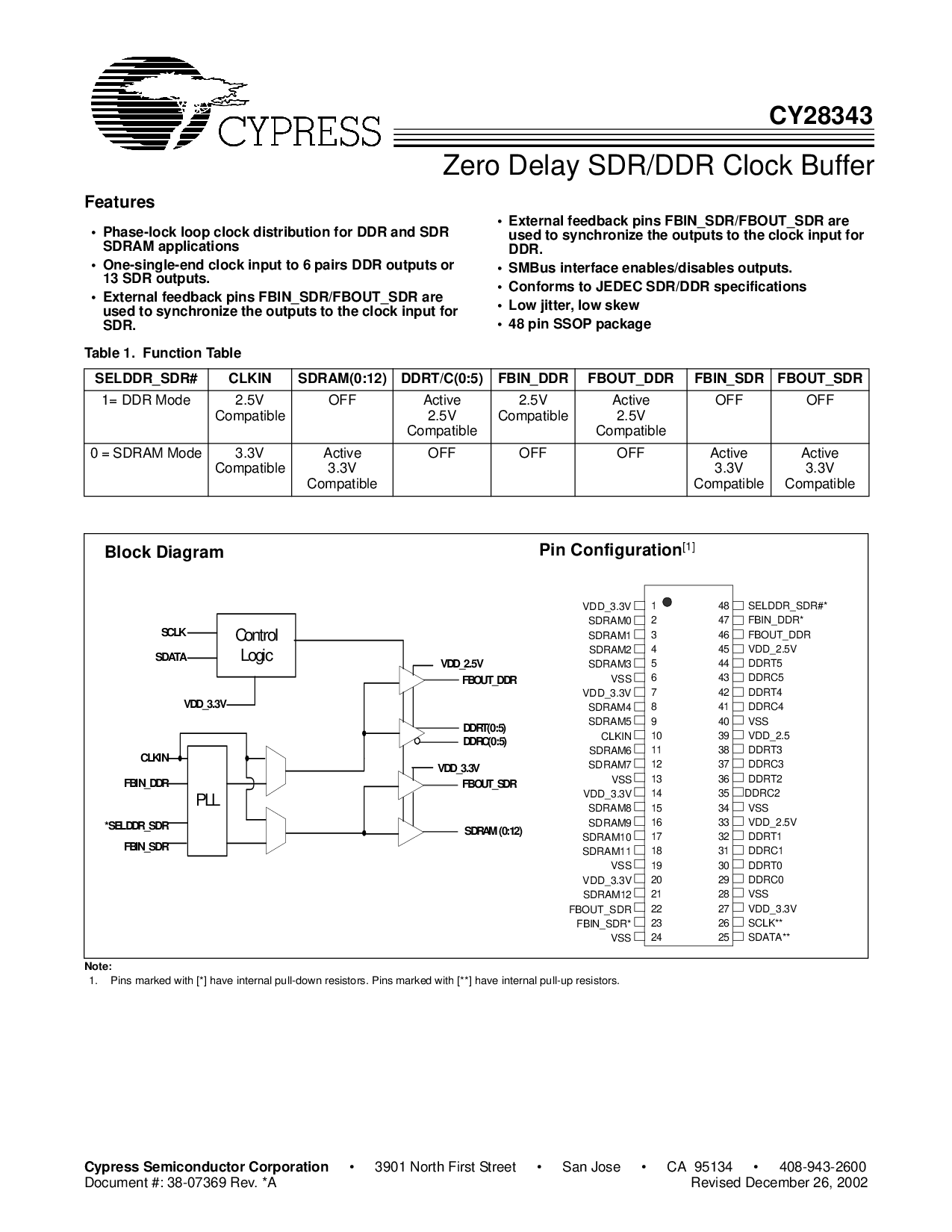

表 1. 功能 表

selddr_sdr# CLKIN sdram(0:12) ddrt/c(0:5) fbin_ddr fbout_ddr fbin_sdr fbout_sdr

1= ddr 模式 2.5v

兼容

关 活动

2.5v

兼容

2.5v

兼容

活动

2.5v

兼容

关 关

0 = sdram 模式 3.3v

兼容

活动

3.3v

兼容

关 关 关 活动

3.3v

兼容

活动

3.3v

兼容

块 图表

管脚 配置

[1]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

vdd_3.3v

SDRAM0

SDRAM1

SDRAM2

SDRAM3

vss

vdd_3.3v

SDRAM4

SDRAM5

CLKIN

SDRAM6

SDRAM7

vss

vdd_3.3v

SDRAM8

SDRAM9

SDRAM10

SDRAM11

vss

vdd_3.3v

SDRAM12

fbout_sdr

fbin_sdr*

vss

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

selddr_sdr#*

fbin_ddr*

fbout_ddr

vdd_2.5v

DDRT5

DDRC5

DDRT4

DDRC4

vss

vdd_2.5

DDRT3

DDRC3

DDRT2

DDRC2

vss

vdd_2.5v

DDRT1

DDRC1

DDRT0

DDRC0

vss

vdd_3.3v

SCLK**

SDATA**

fbout_ddr

ddrt(0:5)

ddrc(0:5)

一氧化碳nt右ol

logic

fbout_sdr

sdram (0: 12)

SCLK

SDATA

PLL

*selddr_sdr

FBIn_ddr

CLKI n

FBIn_sdr

vdd_2.5V

vdd_3.3v

vdd_3.3V