2.5v 或 3.3v, 200-mhz, 9-输出 零 延迟 布菲右

CY29351

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07475 rev. *a 修订 july 26, 2004

特点

• 输出 频率 范围: 25 mhz 至 200 mhz

• 输入 频率 范围: 25 mhz 至 200 mhz

• 2.5v 或 3.3v 操作

• 拆分 2.5v/3.3v 产出

• ±2.5% 最大值 输出 职责 循环 变化

• 9 时钟 产出: 驱动器 向上 至 18 时钟 线条

• 两个 参考 时钟 入点看跌期权: lvpecl 或 lvcmos

• 150-ps 最大值 输出-输出 偏斜

• 锁相 回路 (pll) 旁路 模式

• 传播 aware™

• 输出 启用/禁用

• 引脚兼容 与 mpc9351

• 工业 温度 范围: –40°c 至 +85°c

• 32-管脚 1.0-mm tqfp 包装

功能 描述

这 cy29351 是 一个 低 电压 高 业绩 200 mhz

pll-基于 零 延迟 缓冲区 设计 用于 高 速度 时钟

分布 应用程序.

这 cy29351 特点 lvpecl 和 lvcmos 参考 时钟

输入 和 提供 9 产出 零件itioned 入点 4 银行 的 1, 1, 2,

和 5 产出. 银行 一个 划分 这 vco 输出 由 2 或 4 同时

这 其他 银行 除法 由 4 或 8 按 选择(一个:d) 设置, 请参见

功能 表

. 这些 分隔器 允许 输出 至 输入 比率 的

4:1, 2:1, 1:1, 1:2, 和 1:4.每个 lvcmos 兼容 输出

可以 驱动器 50

Ω

系列 或 平行 已终止 变速器 线条.

用于 系列 已终止 变速器 线条, 每个 输出 可以

驱动器 一个 或 两个 痕迹 给予这 设备 一个 有效 扇出 的

1:18.

这 pll 是 确保 稳定 给定 那 这 vco 是 已配置 至

运行 之间 200 mhz 至 500 mhz. 这个 允许 一个 宽 范围

的 输出 频率 从 25 mhz 至 200 mhz. 用于 正常

操作, 这 外部 反馈输入, fb_入点, 是 已连接 至

一个 的 这 产出. 这 内部 vco 是 正在运行 在 倍数 的

这 输入 参考 时钟 设置 由 这 反馈 分隔器, 请参见 这

助教ble? 1.

当 pll_en 是 低, pll 是 旁路 和 这 参考

时钟 直接 饲料 这 输出 分隔器. 这个 模式 是 完全 静态

和 这 最小值 输入 时钟 频率 规格 是否 不

应用.

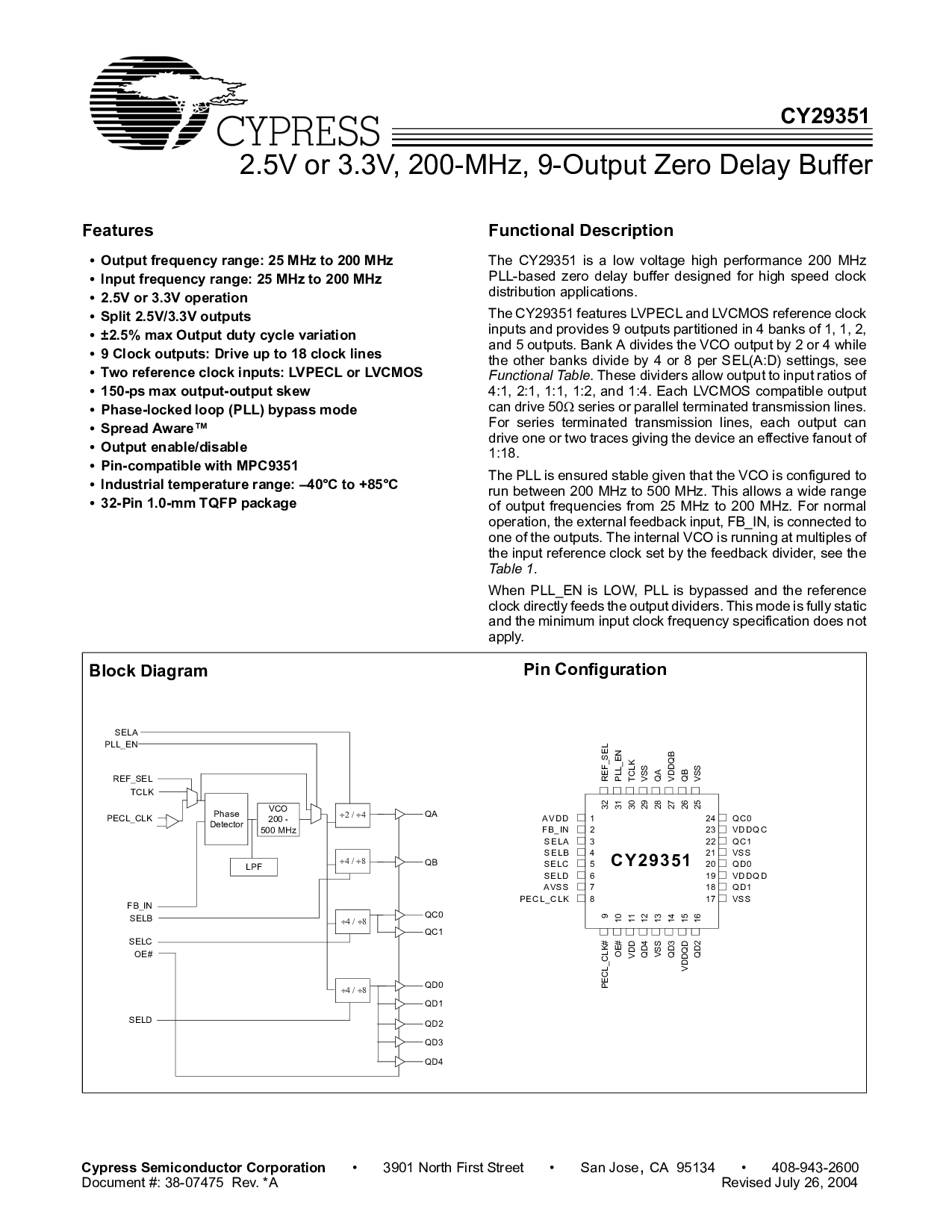

块 图表

管脚 配置

相位

检测器

LPF

÷2 / ÷4

÷4 / ÷8

÷4 / ÷8

÷4 / ÷8

QA

QB

QC0

QC1

QD0

QD1

QD2

QD3

QD4

SELA

pll_en

TCLK

参考_选择

pecl_clk

fb_入点

SELB

SELC

OE#

SELD

VCO

200 -

500 mhz

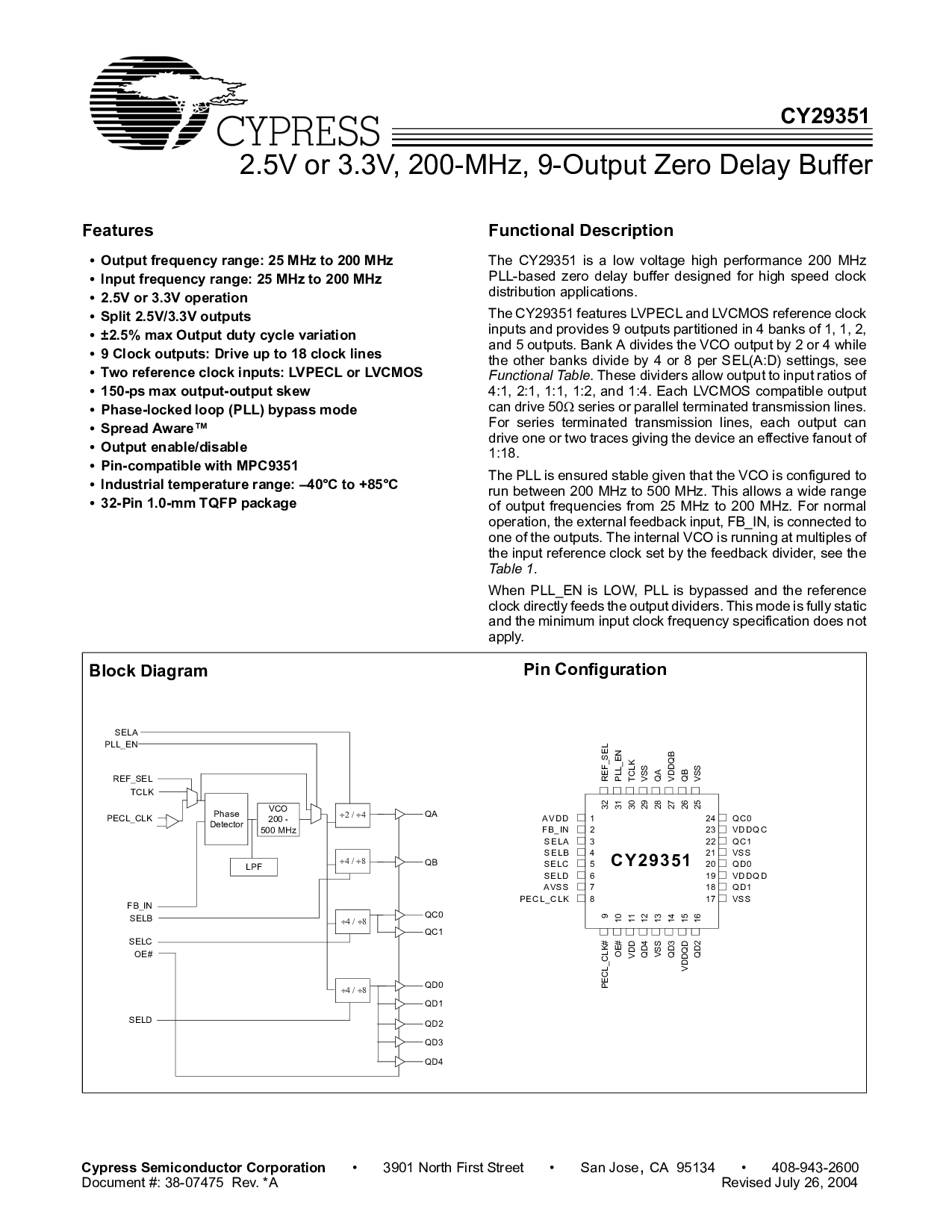

CY29351

参考_选择

pll_en

TCLK

vss

QA

VDDQB

QB

vss

pecl_clk#

OE#

VDD

QD4

vss

QD3

VDDQD

QD2

QC0

VDDQC

QC1

vss

QD0

VDDQD

QD1

vss

AVDD

fb_入点

SELA

SELB

SELC

SELD

AVSS

pecl_clk

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25