3.3v 125-mhz 多-output 零 延迟 布菲右

CY29973

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07291 rev. *b 修订 january 19, 2004

特点

• 输出 频率 向上 至 125 mhz

• 12 时钟 产出: 频率 可配置

• 350-ps 最大值 输出 至 输出 偏斜

• 可配置 输出 禁用

• 两个 参考 时钟 输入 用于 动态 切换

• 振荡器 或 pecl 参考 输入

• 传播 光谱 兼容

• 无故障 输出 时钟 过渡

• 3.3v 电源 供应

• 管脚 兼容 与 mpc973

• 工业 温度 右心房ng: –40°c 至 +85°c

• 52-管脚 tqfp 包装

备注:

1. x = 这 参考 输入 频率, 200 mhz &指示灯; f

VCO

&指示灯; 480 mhz.

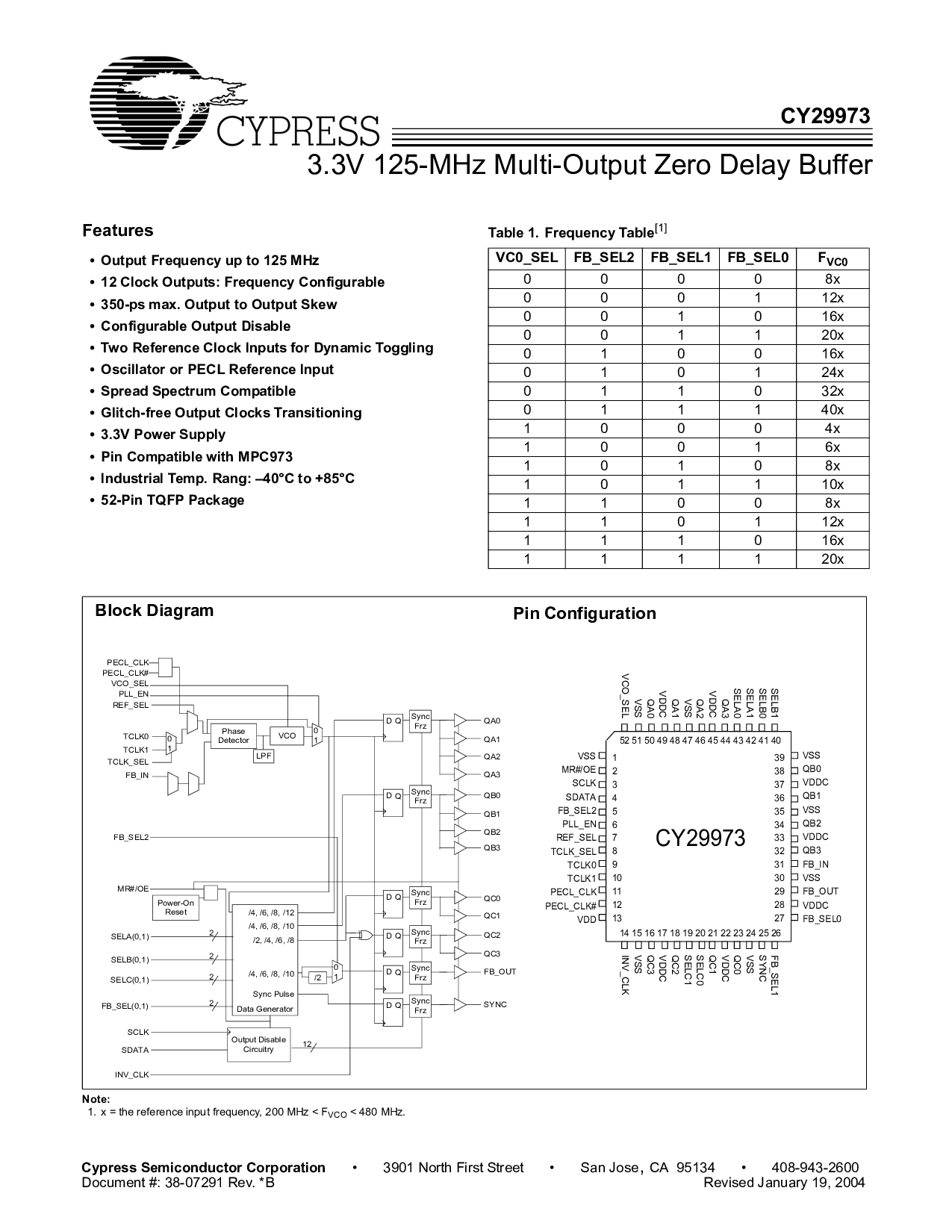

表 1. 频率 表

[1]

vc0_选择 fb_sel2 fb_sel1 fb_sel0 f

VC0

00008x

000112x

001016x

001120x

010016x

010124x

011032x

011140x

10004x

10016x

10108x

101110x

11008x

110112x

111016x

111120x

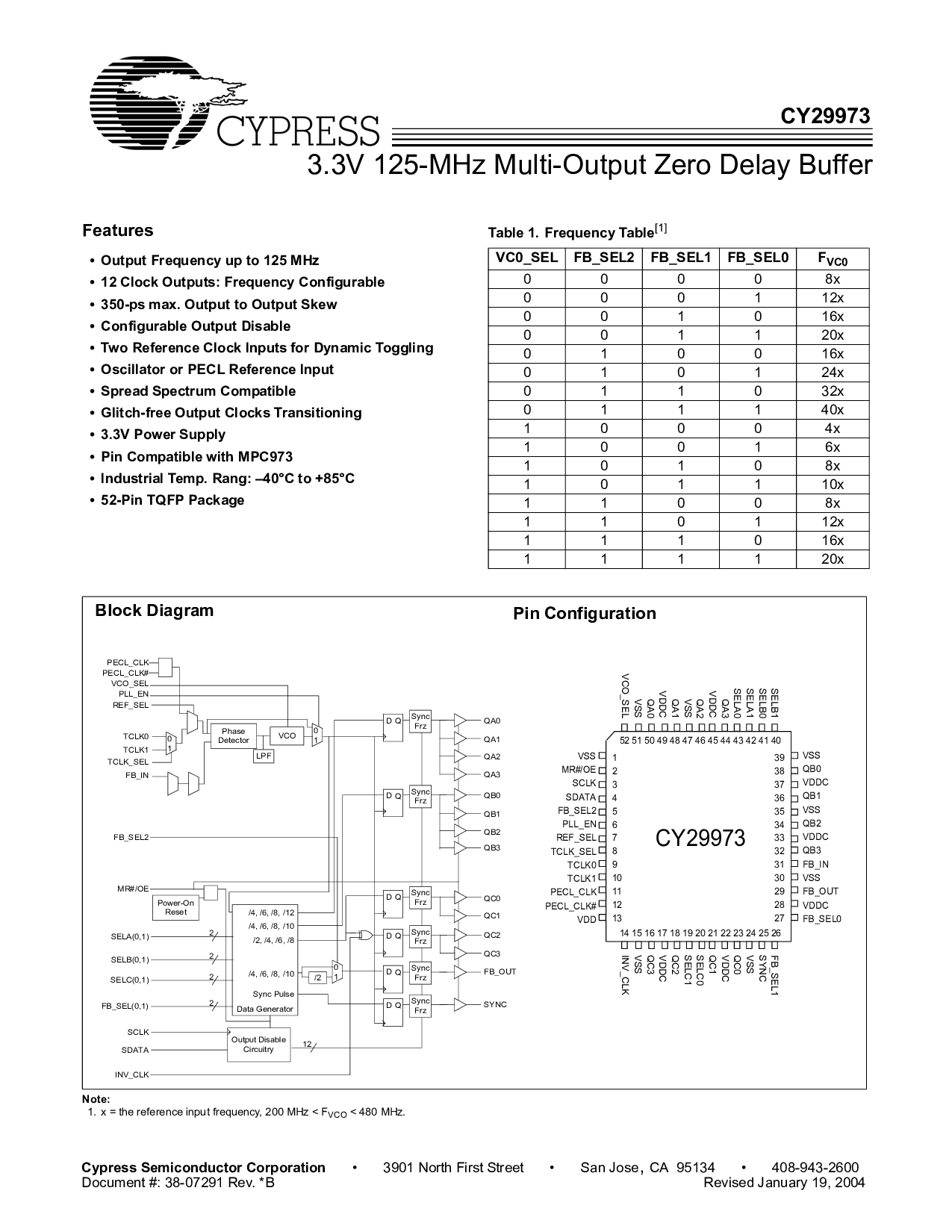

blockdi图

管脚 配置

参考_选择

0

1

0

1

相位

检测器

VCO

LPF

同步

Frz

d

q

QA0

同步

Frz

d

q

同步

Frz

d

q

同步

Frz

d

q

同步

Frz

d

q

同步

Frz

d

q

0

1

/2

通电

重置

输出 禁用

电路

数据 发电机

/4, /6, /8, /12

/4, /6, /8, /10

/2, /4, /6, /8

/4, /6, /8, /10

同步 脉冲

pecl_clk

pecl_clk#

TCLK0

TCLK1

tclk_选择

fb_入点

fb_sel2

mr#/oe

sela(0,1)

2

selb(0,1)

2

selc(0,1)

2

fb_选择(0,1)

2

SCLK

SDATA

inv_clk

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QC2

QC3

fb_出点

同步

12

vco_选择

pll_en

vss

mr#/oe

SCLK

SDATA

fb_sel2

pll_en

参考_选择

tclk_选择

TCLK0

TCLK1

pecl_clk

pecl_clk#

VDD

fb_sel1

同步

vss

QC0

VDDC

QC1

SELC0

SELC1

QC2

VDDC

QC3

vss

inv_clk

SELB1

SELB0

SELA1

SELA0

QA3

VDDC

QA2

vss

QA1

VDDC

QA0

vss

vco_选择

vss

QB0

VDDC

QB1

vss

QB2

VDDC

QB3

fb_入点

vss

fb_出点

VDDC

fb_sel0

1

2

3

4

5

6

7

8

9

10

11

12

13

39

38

37

36

35

34

33

32

31

30

29

28

27

14 15 16 17 18 19 20 21 22 23 24 25 26

52 51 50 49 48 47 46 45 44 43 42 41 40

CY29973