© 1999 仙童 半导体 公司 DS009473 www.仙女半.com

april 1988

修订 july 1999

74f113 双 jk 负 边沿触发 触发器

74F113

双 jk 负 边沿触发 触发器

概述 描述

这 74f113 优惠 个人 j, k, 设置 和 时钟 输入.

当 这 时钟 去 高 这 输入 是 已启用 和

数据 将 是 已输入. 这 逻辑 水平 的 这 j 和 k 输入

将 是 已更改 当 这 时钟 脉冲 是 高 和 这 翻转-

翻牌圈 将 执行 根据 至 这 真相 表 作为 长 作为

最小值 设置 和 保持 次 是 观察到的. 输入 数据 是

已转移 至 这 产出 开启 这 坠落 边缘 的 这 时钟

脉冲.

异步 输入:

低 输入 至 s

d

集 q 至 高 水平

设置 是 独立 的 时钟

订购 代码:

设备 也 可用 入点 胶带 和 卷轴. 指定 由 追加 这 后缀 信函 “x” 至 这 订购 代码.

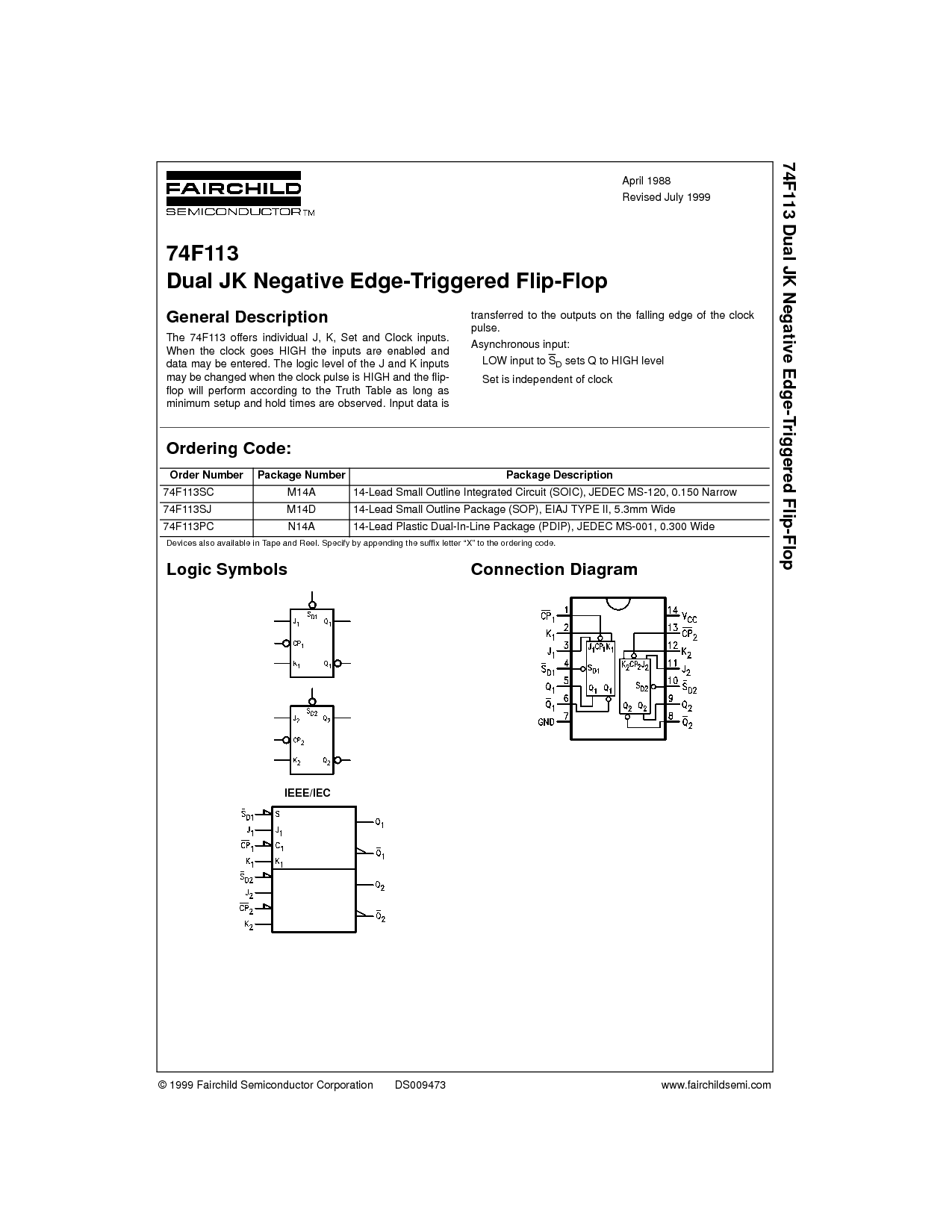

逻辑 符号

ieee/iec

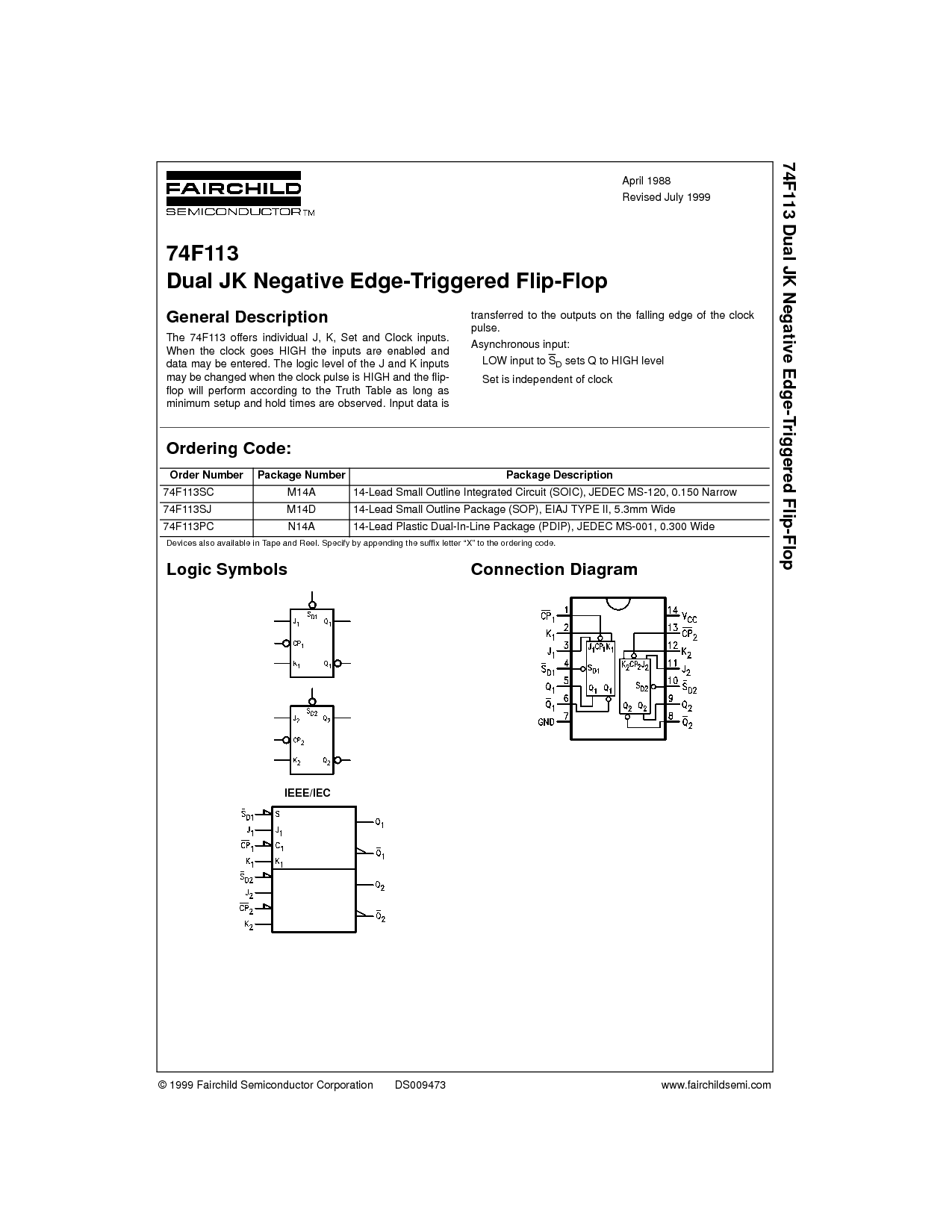

连接 图表

订单 号码 包装 号码 包装 描述

74F113SC M14A 14-铅 小 大纲 综合 电路 (soic), 电子元件工业联合会 ms-120, 0.150 窄

74F113SJ M14D 14-铅 小 大纲 包装 (sop), eiaj 类型 二, 5.3mm 宽

74F113PC N14A 14-铅 塑料 双列直插式 包装 (pdip), 电子元件工业联合会 ms-001, 0.300 宽