ics650-12

mpeg 时钟 合成器

mds 650-12 一个

1

修订 113000

综合 电路 系统, 公司 • 525 种族 街道 • san jose •ca•95126• (408) 295-9800tel • www.icst.com

这 ics650-12 是 一个 低 成本, 低 抖动, 高

业绩 时钟 合成器 设计 至

生产 固定 时钟 产出 的 13.5 mhz 和

27.0 mhz 和 四 可选择 时钟 产出 的 两个

处理器 时钟 (pclk1 和 pclk2), 音频

时钟 (aclk), 和 通信 时钟

(cclk). 使用 我们的 专利 模拟 相位-

已锁定 回路 (pll) 技术, 这 设备 用途 一个

27.0 mhz 时钟 或 基本面 水晶 输入 至

生产 时钟 理想 用于 数字 视频/mpeg-

基于 应用程序.

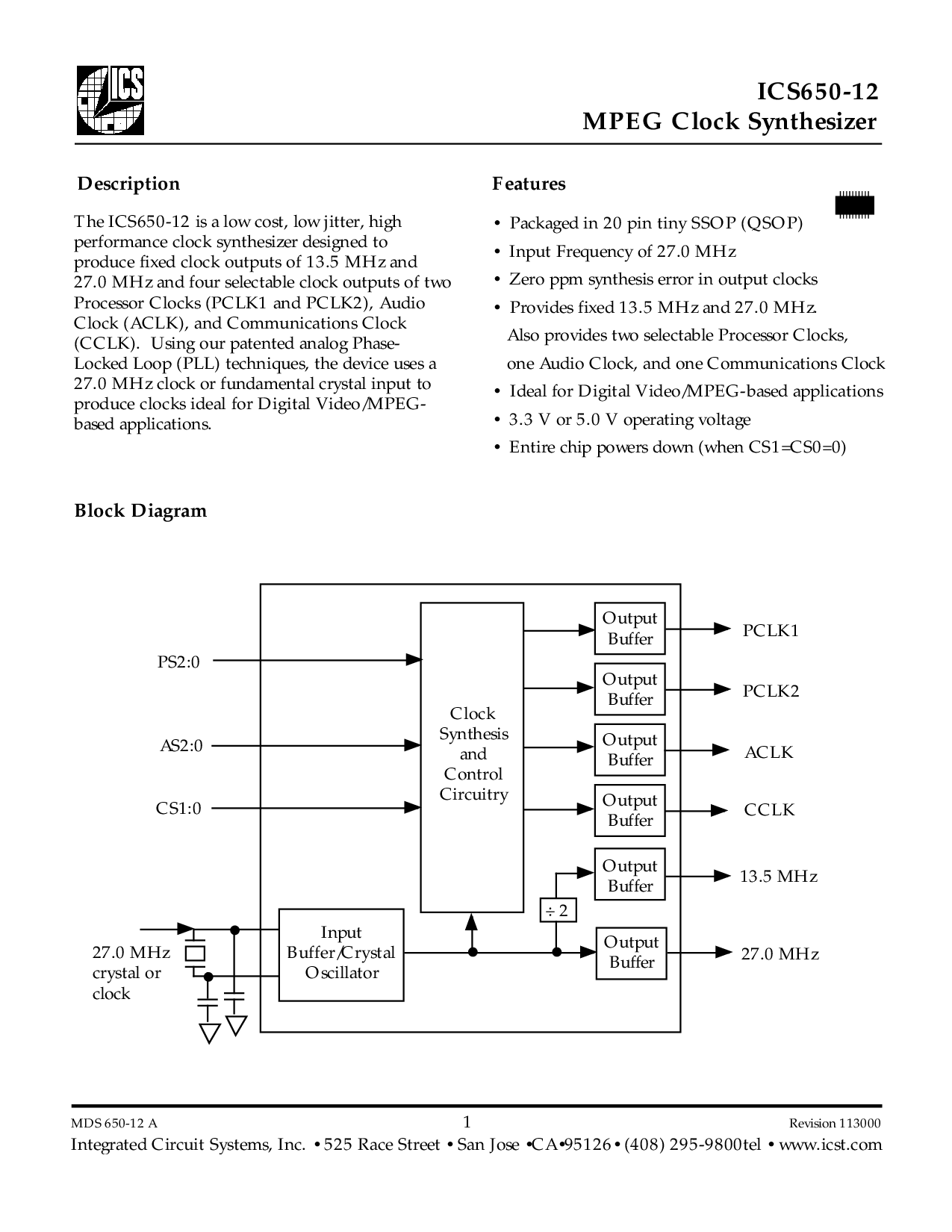

块 图表

描述 特点

• 已打包 入点 20 管脚 微小的 ssop (qsop)

• 输入 频率 的 27.0 mhz

• 零 ppm 合成 错误 入点 输出 时钟

• 提供 固定 13.5 mhz 和 27.0 mhz.

也 提供 两个 可选择 处理器 时钟,

一个 音频 时钟, 和 一个 通信 时钟

• 理想 用于 数字 视频/mpeg-基于 应用程序

• 3.3 v 或 5.0 v 操作 电压

• 整个 芯片 权力 向下 (当 cs1=cs0=0)

13.5 mhz

输入

缓冲区/水晶

振荡器

时钟

合成

和

控制

电路

输出

缓冲区

输出

缓冲区

输出

缓冲区

27.0 mhz

输出

缓冲区

输出

缓冲区

cs1:0

27.0 mhz

水晶 或

时钟

PCLK2

ACLK

CCLK

as2:0

ps2:0

输出

缓冲区

PCLK1

÷ 2