综合

电路

系统, 公司

ICS93725

0606a—08/01/03

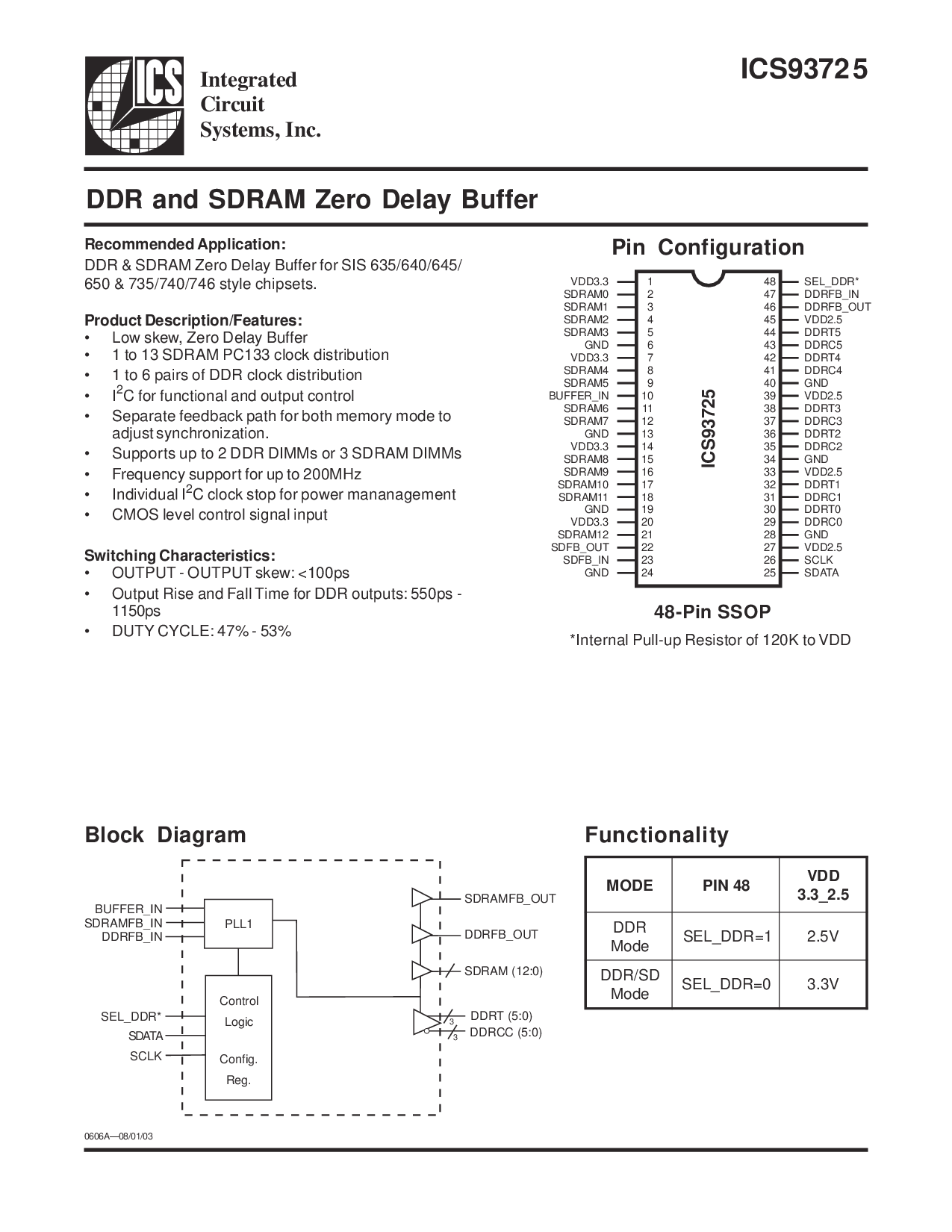

块 图表

ddr 和 sdram 零 延迟 缓冲区

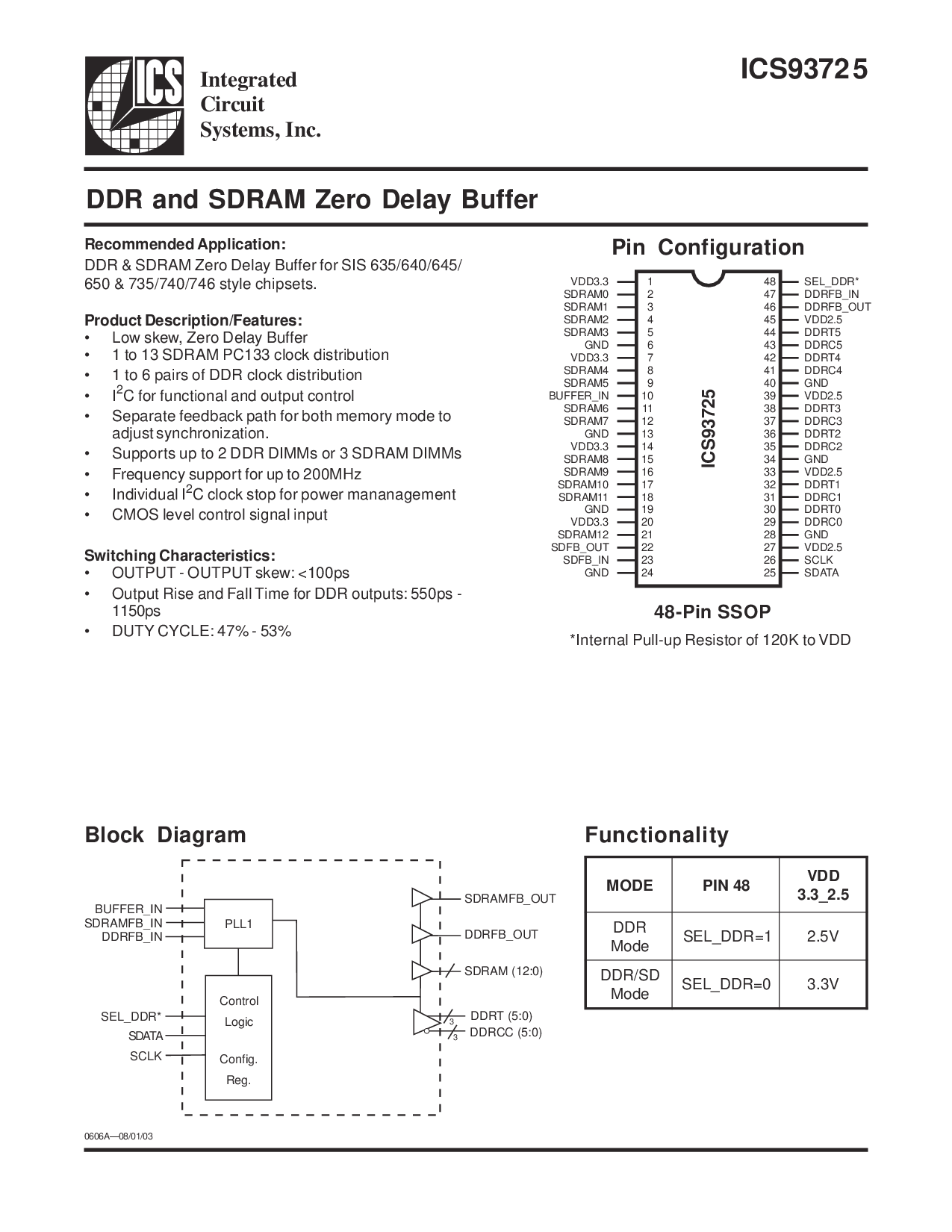

管脚 配置

48-管脚 ssop

推荐 应用程序:

ddr &放大器; sdram 零 延迟 缓冲区 用于 sis 635/640/645/

650 &放大器; 735/740/746 风格 chipsets.

产品 描述/特点:

• 低 偏斜, 零 延迟 缓冲区

• 1 至 13 sdram pc133 时钟 分布

• 1 至 6 对 的 ddr 时钟 分布

•I

2

c 用于 功能 和 输出 控制

• 分开 反馈 路径 用于 两者都有 记忆 模式 至

调整 同步.

• 支架 向上 至 2 ddr dimms 或 3 sdram dimms

• 频率 支持 用于 向上 至 200mhz

• 个人 我

2

c 时钟 停止 用于 电源 mananagement

• cmos 水平 控制 信号 输入

开关 特性:

• 输出 - 输出 偏斜: &指示灯;100ps

• 输出 上升 和 坠落 时间 用于 ddr 产出: 550ps -

1150ps

• 职责 循环: 47% - 53%

*internal 上拉 电阻 的 120k 至 vdd

功能

EDOM84NIP

DDV

5.2_3.3

RDD

以东

1=rdd_乐SV5.2

ds/rdd

以东

0=rdd_乐SV3.3

vdd3.3

SDRAM0

SDRAM1

SDRAM2

SDRAM3

地

vdd3.3

SDRAM4

SDRAM5

缓冲区_入点

SDRAM6

SDRAM7

地

vdd3.3

SDRAM8

SDRAM9

SDRAM10

SDRAM11

地

vdd3.3

SDRAM12

sdfb_出点

sdfb_入点

地

选择_ddr*

ddrfb_入点

ddrfb_出点

vdd2.5

DDRT5

DDRC5

DDRT4

DDRC4

地

vdd2.5

DDRT3

DDRC3

DDRT2

DDRC2

地

vdd2.5

DDRT1

DDRC1

DDRT0

DDRC0

地

vdd2.5

SCLK

sdata

ICS93725

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

选择_ddr*

PLL1

sdram (12:0)

ddrfb_出点

sdramfb_出点

缓冲区_入点

sdramfb_入点

ddrfb_入点

SDATA

SCLK

控制

逻辑

配置.

注册.

3

3

ddrt (5:0)

ddrcc (5:0)