综合

电路

系统, 公司

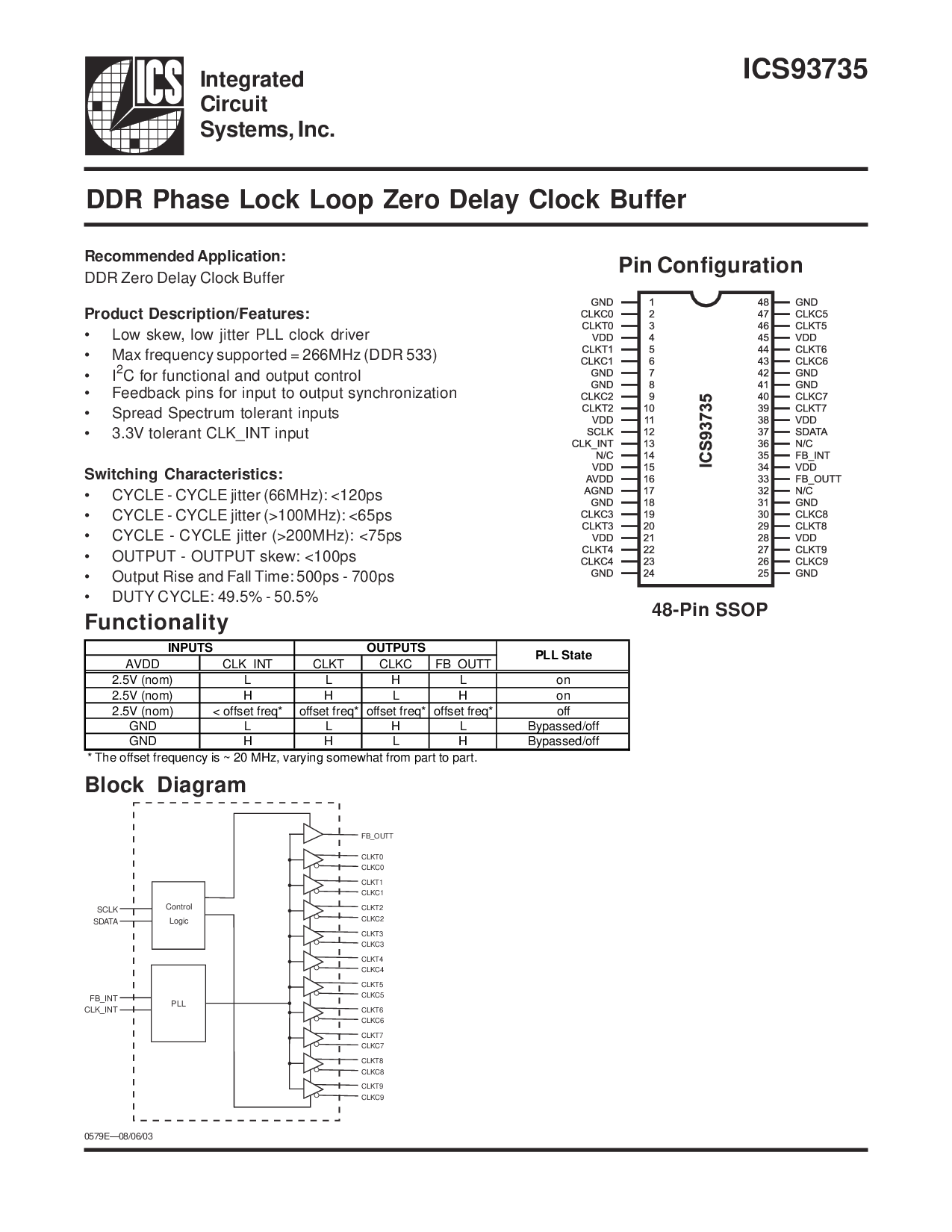

ICS93735

0579e—08/06/03

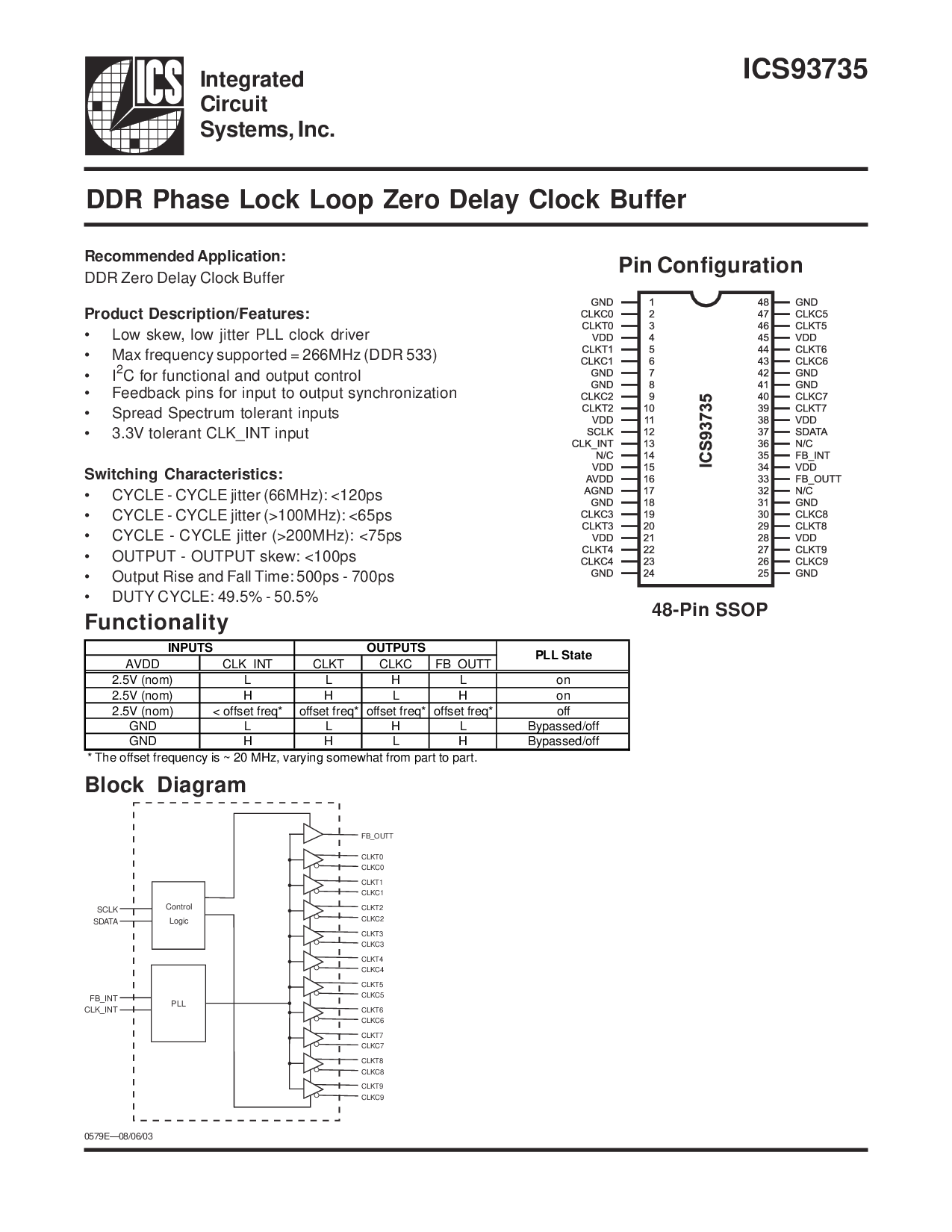

块 图表

ddr 相位 锁 回路 零 延迟 时钟 缓冲区

管脚 配置

48-管脚 ssop

推荐 应用程序:

ddr 零 延迟 时钟 缓冲区

产品 描述/特点:

• 低 偏斜, 低 抖动 pll 时钟 驾驶员

• 最大值 频率 支持 = 266mhz (ddr 533)

•I

2

c 用于 功能 和 输出 控制

• 反馈 针脚 用于 输入 至 输出 同步

• 传播 光谱 宽容 输入

• 3.3v 宽容 clk_智力 输入

开关 特性:

• 循环 - 循环 抖动 (66mhz): &指示灯;120ps

• 循环 - 循环 抖动 (>100mhz): &指示灯;65ps

• 循环 - 循环 抖动 (>200mhz): &指示灯;75ps

• 输出 - 输出 偏斜: &指示灯;100ps

• 输出 上升 和 坠落 时间: 500ps - 700ps

• 职责 循环: 49.5% - 50.5%

功能

fb_智力

clk_智力

PLL

SCLK

s 数据

控制

逻辑

fb_outt

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

AVDD clk_智力 CLKT CLKC fb_outt

2.5v (nom) l l h l 开启

2.5v (nom) h h l h 开启

2.5v (nom) &指示灯; 偏移量 freq* 偏移量 freq* 偏移量 freq* 偏移量 freq* 关

地 l l h l B

y通过/关

地 h h l h 旁路/关

* 这 偏移量 频率 是 ~ 20 mhz, 变化 有点 从 零件 至 零件.

输入 产出

pll 州