1/12九月 2004

■

5v 宽容 输入

■

高 速度:

t

pd

= 6.7ns (最大值.) 在 v

抄送

= 3v

■

电源 向下 保护 开启 输入

和 产出

■

对称 输出 阻抗:

|I

哦

| = 我

ol

= 24ma (最小) 在 v

抄送

= 3v

■

pci 总线 级别 保证 在 24 ma

■

平衡式 传播 延误:

t

PLH

≅

t

PHL

■

操作 电压 范围:

v

抄送

(opr) = 2.0v 至 3.6v (1.5v 数据

保留)

■

管脚 和 功能 兼容 与

74 系列 138

■

闩锁 业绩 超过

500ma (jesd 17)

■

esd 业绩:

hbm > 2000v (密耳 标准 883 方法 3015);

mm > 200v

描述

这 74lcx138 是 一个 低 电压 cmos 3 至 8

线 解码器 (反转) 预制 与

亚微米 硅 闸门 和 双层 金属

接线 c

2

mos 技术. 它 是 理想 用于 低 电源

和 高 速度 3.3v 应用程序; 它 可以 是

接口 至 5v 信号 环境 用于 输入.

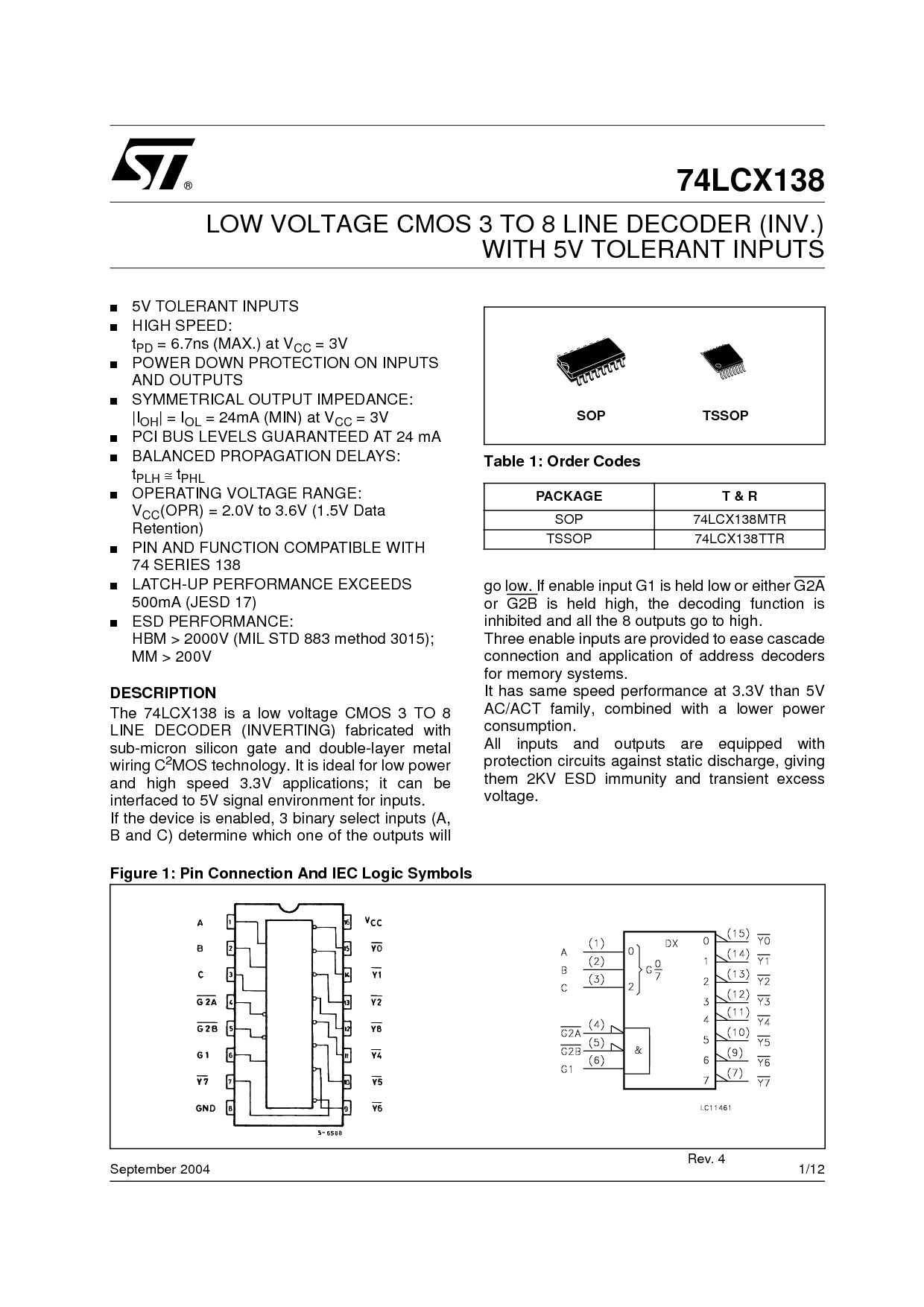

如果 这 设备 是 已启用, 3 二进制 选择 输入 (一个,

b 和 c) 确定 哪个 一个 的 这 产出 将

走 低. 如果 启用 输入 g1 是 持有 低 或 要么 g2a

或 g2b是 持有 高, 这 解码 功能 是

抑制 和 全部 这 8 产出 走 至 高.

三个 启用 输入 是 提供 至 轻松 级联

连接 和 应用程序 的 地址 解码器

用于 记忆 系统.

它 有 相同 速度 业绩 在 3.3v 比 5v

交流电/act 家庭, 合并 与 一个 下部 电源

消费.

全部 输入 和 产出 是 配备 与

保护 电路 反对 静态 放电, 给予

他们 2kv esd 免疫 和 瞬态 超额

电压.

74LCX138

低 电压 cmos 3 至 8 线 解码器 (inv.)

与 5v 宽容 输入

图 1: 管脚 连接 和 iec 逻辑 符号

表 1: 订单 代码

包装 t &放大器; 右

SOP 74LCX138MTR

TSSOP 74LCX138TTR

TSSOPSOP

rev. 4