1

特性

•

串行 附带的 接口 (spi) 兼容

•

支持 spi 模式 0 (0,0) 和 3 (1,1)

•

10 mhz 时钟 比率

•

128-字节 页 模式 仅有的 为 写 行动

•

低-电压 和 标准-电压 运作

– 5.0 (v

CC

= 4.5v 至 5.5v)

– 2.7 (v

CC

= 2.7v 至 5.5v)

– 1.8 (v

CC

= 1.8v 至 3.6v)

•

块 写 保护

– 保护 1/4, 1/2, 或者 全部 排列

•

写 保护 (wp) 管脚 和 写 使不能运转 说明 为

两个都 硬件 和 软件 数据 保护

•

高 可靠性

– 忍耐力: 100k 写 循环

– 数据 保持: > 40 年

– 静电释放 保护: > 3000v

•

8-管脚 pdip, 8-管脚 eiaj soic, 和 8-pin 无铅 排列 包装

描述

这 at25hp256/512 提供 262,144/524,288 位 的 串行 用电气 可擦掉的 pro-

grammable 读 仅有的 记忆 (可擦可编程只读存储器) 有组织的 作 32,768/65,536 words 的 8-位

各自. 这 设备 是 优化 为 使用 在 许多 工业的 和 商业的 产品

在哪里 高-速, 低-电源, 和 低-电压 运作 是 essential. 这

at25hp256/512 是 有 在 一个 空间 节省 8-管脚 pdip (at25hp256/512), 8-管脚

eiaj soic (at25hp256), 和 8-管脚 无铅 排列 (at25hp256/512) 包装. 在

rev. 1113b–07/98

spi 串行

EEPROMs

256k (32,768 x 8)

512k (65,536 x 8)

AT25HP256

AT25HP512

初步的

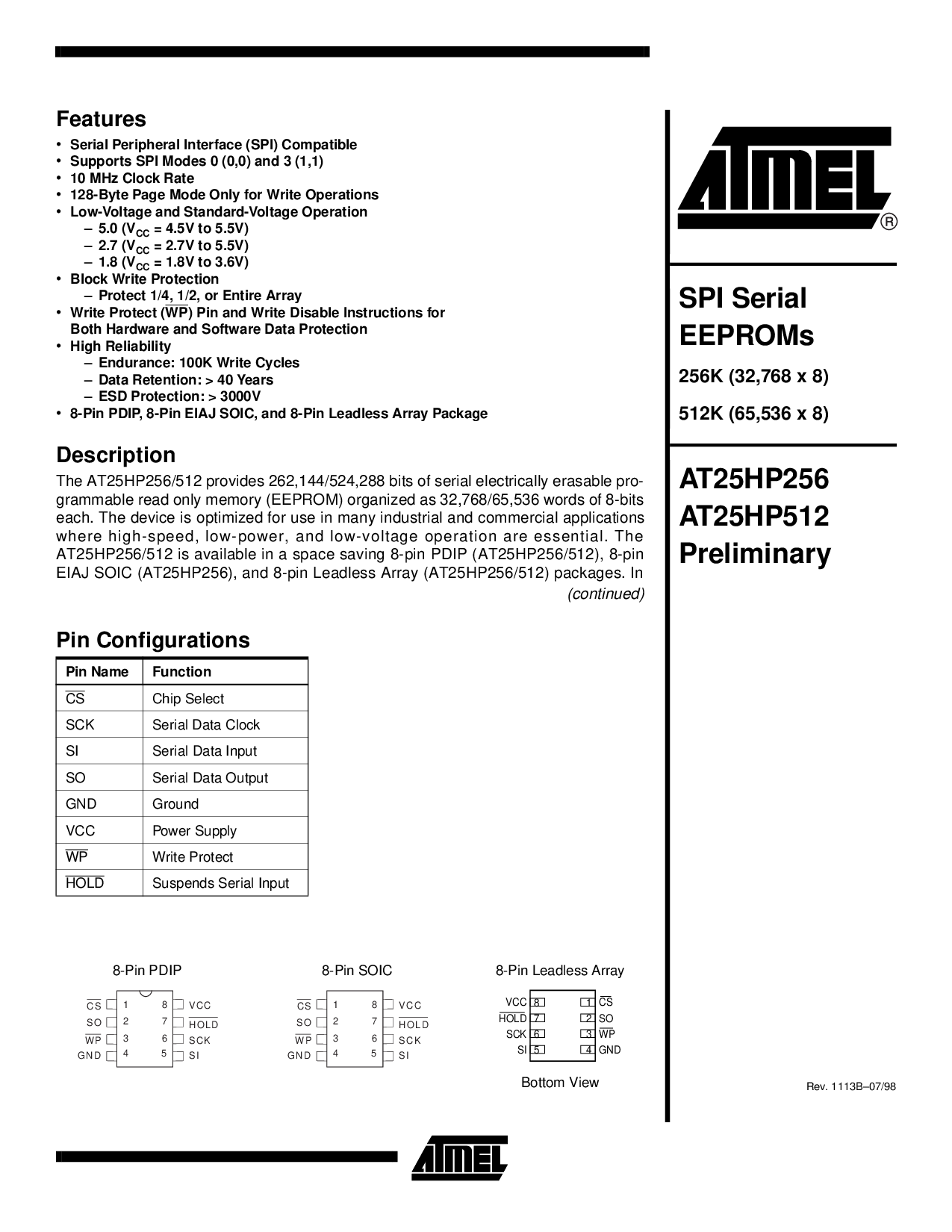

管脚 配置

管脚 名字 函数

CS

碎片 选择

SCK 串行 数据 时钟

SI 串行 数据 输入

所以 串行 数据 输出

地 地面

VCC 电源 供应

WP

写 保护

支撑 suspends 串行 输入

(持续)

8-管脚 soic

CS

SCK

所以

WP

支撑

地

VCC

1

2

3

4

8

7

6

5

SI

8-管脚 pdip

CS

SCK

所以

WP

支撑

地

VCC

1

2

3

4

8

7

6

5

SI

8-管脚 无铅 排列

bottom 视图

1

2

3

4

8

7

6

5

VCC

支撑

SCK

SI

CS

所以

WP

地