rev. d

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个将结果从它的使用.非执照是准予用牵涉或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

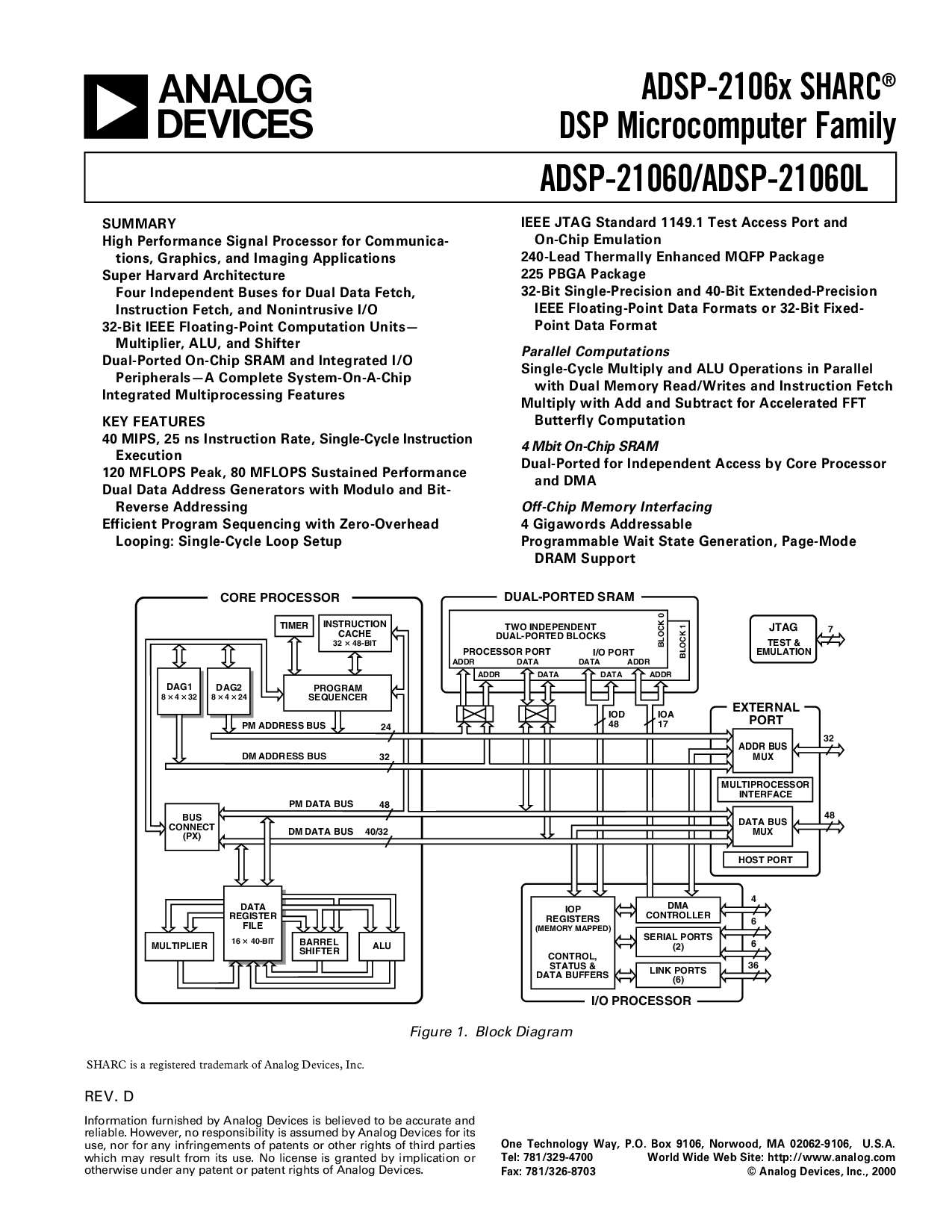

adsp-2106x sharc

®

dsp microcomputer 家族

adsp-21060/adsp-21060l

ieee jtag 标准 1149.1 测试 进入 端口 和

在-碎片 emulation

240-含铅的 thermally 增强 mqfp 包装

225 pbga 包装

32-位 单独的-精确 和 40-位 扩展-精确

ieee floating-要点 数据 formats 或者 32-位 fixed-

要点 数据 format

并行的 computations

单独的-循环 乘以 和 alu 行动 在 并行的

和 双 记忆 读/写 和 操作指南 fetch

乘以 和 增加 和 减去 为 accelerated fft

butterfly computation

4 mbit 在-碎片 sram

双-ported 为 独立 进入 用 核心 处理器

和 dma

止-碎片 记忆 接合

4 gigawords addressable

可编程序的 wait 状态 一代, 页-模式

dram 支持

sharc 是 一个 注册 商标 的 相似物 设备, 公司

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 2000

SUMMARY

高 效能 信号 处理器 为 communica-

tions, graphics, 和 imaging 产品

超级的 harvard architecture

四 独立 buses 为 双 数据 fetch,

操作指南 fetch, 和 nonintrusive i/o

32-位 ieee floating-要点 computation units—

乘法器, alu, 和 shifter

双-ported 在-碎片 sram 和 整体的 i/o

peripherals—a 完全 系统-在-一个-碎片

整体的 multiprocessing 特性

关键 特性

40 mips, 25 ns 操作指南 比率, 单独的-循环 操作指南

执行

120 mflops 顶峰, 80 mflops sustained 效能

双 数据 地址 发生器 和 modulo 和 位-

反转 寻址

效率高的 程序 sequencing 和 零-overhead

looping: 单独的-循环 循环 建制

数据

寄存器

文件

16

40-位

BARREL

SHIFTER

ALU乘法器

7

JTAG

测试 &放大;

EMULATION

32

48

地址 总线

MUX

数据 总线

MUX

MULTIPROCESSOR

接口

host 端口

外部

端口

4

6

6

36

IOP

寄存器

(记忆 编排)

控制,

状态 &放大;

数据 缓存区

i/o 处理器

link 端口

(6)

串行 端口

(2)

DMA

控制

IOA

17

IOD

48

地址 数据

块 1

ADDRDATA

ADDRDATAADDR 数据

二 独立

双-ported blocks

块 0

处理器 端口

i/o 端口

双-ported sram

24

32

48

40/32

程序

SEQUENCER

操作指南

CACHE

32

48-位

计时器

总线

连接

(px)

pm 数据 总线

dm 数据 总线

dm 地址 总线

pm 地址 总线

DAG1

8

4

32

DAG2

8

4

24

核心 处理器

图示 1. 块 图解