2032e_03

1

ispLSI

®

2032E

在-系统 可编程序的

superfast™ 高 密度 pld

特性

• superfast 高 密度 在-系统

可编程序的 逻辑

— 1000 pld 门

— 32 i/o 管脚, 二 专心致志的 输入

— 32 寄存器

— 高 速 global interconnect

— 宽 输入 gating 为 快 counters, 状态

machines, 地址 decoders, 等

— 小 逻辑 块 大小 为 随机的 逻辑

— 100% functionally 和 电子元件工业联合会 upward 兼容

和 isplsi 2032 设备

• 高 效能 e

2

CMOS

®

技术

—

f

最大值

= 225 mhz 最大 运行 频率

—

t

pd

= 3.5 ns 传播 延迟

— ttl 兼容 输入 和 输出

— 5v 可编程序的 逻辑 核心

— ispjtag™ 在-系统 可编程序的 通过 ieee 1149.1

(jtag) 测试 进入 端口

— 用户-可选择的 3.3v 或者 5v i/o (48-管脚 包装 only)

支持 mixed 电压 系统

— pci 兼容 输出 (48-管脚 包装 仅有的)

— 打开-流 输出 选项

— 用电气 可擦掉的 和 reprogrammable

— 非-易变的

— unused 产品 期 关闭 saves 电源

• isplsi 提供 这 下列的 增加 特性

— 增加 制造 产量, 减少 时间-至-

market 和 改进 产品 质量

— reprogram 焊接 设备 为 faster prototyping

• 提供 这 使容易 的 使用 和 快 系统

速 的 plds 和 这 密度 和 flexibility

的 地方 可编程序的 门 arrays

— 完全 可编程序的 设备 能 联合的 glue

逻辑 和 structured 设计

— 增强 管脚 locking 能力

— 三 专心致志的 时钟 输入 管脚

— 同步的 和 异步的 clocks

— 可编程序的 输出 回转 比率 控制 至

降低 切换 噪音

— 有伸缩性的 管脚 placement

— 优化 global routing pool 提供 global

Interconnectivity

• ispdesignexpert™ – 逻辑 compiler 和 com-

plete isp 设备 设计 系统 从 hdl

综合 通过 在-系统 程序编制

— 更好的 质量 的 结果

— tightly 整体的 和 leading cae vendor tools

— productivity enhancing 定时 分析器, explore

tools, 定时 simulator 和 ispanalyzer™

— pc 和 unix platforms

版权 © 1999 lattice 半导体 corp. 所有 brand 或者 产品 names 是 商标 或者 注册 商标 的 它们的 各自的 holders. 这 规格 和 信息 在此处 是 主题

至 改变 没有 注意.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

Tel. (503) 268-8000; 1-800-l一个ttice;Fax (503) 268-8556; http://www.latticesemi.com

六月 1999

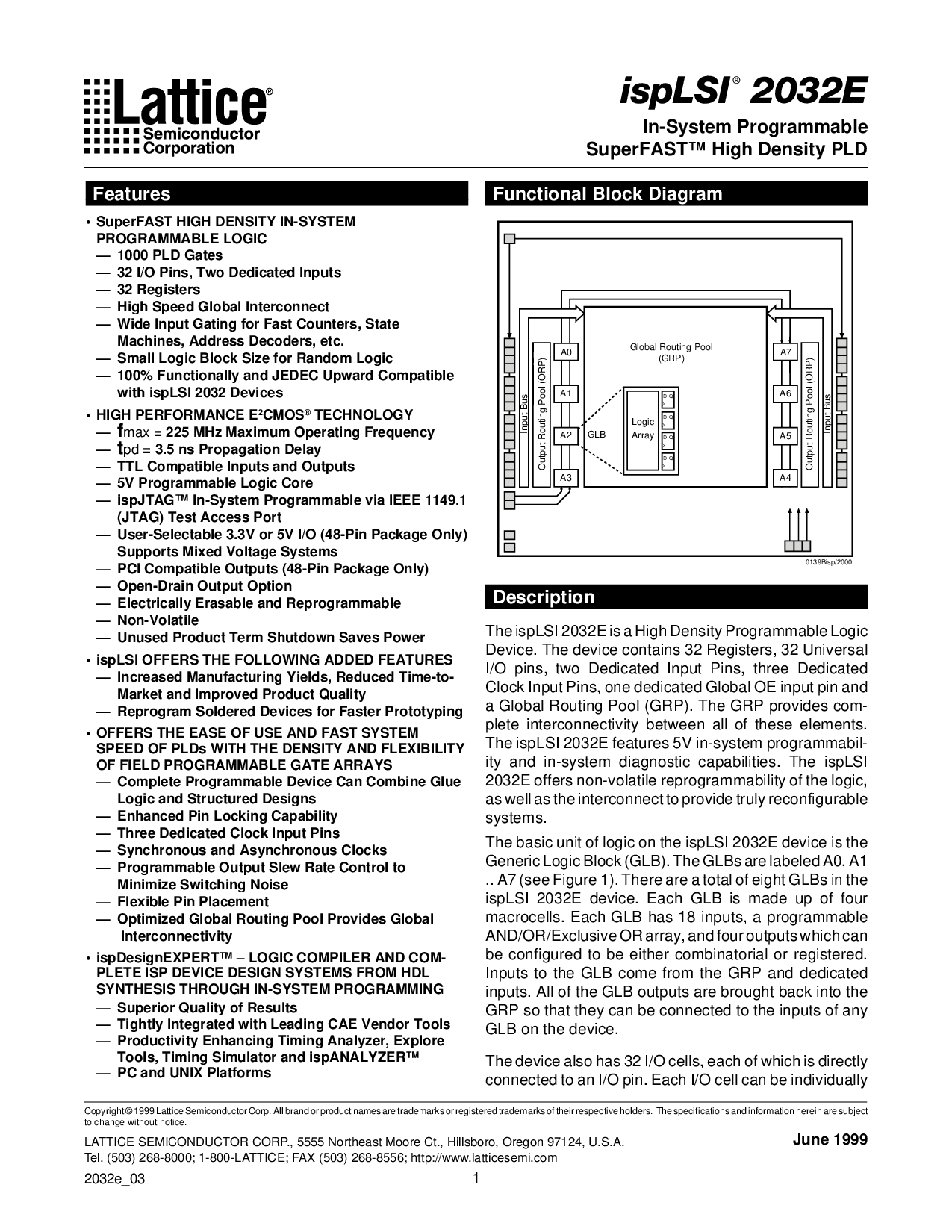

函数的 块 图解

global routing pool

(grp)

A0

A1

A3

输入 总线

输出 routing pool (orp)

A7

A6

A5

A4

输入 总线

输出 routing pool (orp)

A2

GLB

逻辑

排列

DQ

DQ

DQ

DQ

0139bisp/2000

描述

这 isplsi 2032e 是 一个 高 密度 可编程序的 逻辑

设备. 这 设备 包含 32 寄存器, 32 普遍的

i/o 管脚, 二 专心致志的 输入 管脚, 三 专心致志的

时钟 输入 管脚, 一个 专心致志的 global oe 输入 管脚 和

一个 global routing pool (grp). 这 grp 提供 com-

plete interconnectivity 在 所有 的 这些 elements.

这 isplsi 2032e 特性 5v 在-系统 programmabil-

ity 和 在-系统 diagnostic 能力. 这 isplsi

2032e 提供 非-易变的 reprogrammability 的 这 逻辑,

作 好 作 这 interconnect 至 提供 truly reconfigurable

系统.

这 基本 单位 的 逻辑 在 这 isplsi 2032e 设备 是 这

generic 逻辑 块 (glb). 这 glbs 是 labeled a0, a1

.. a7 (看 图示 1). 那里 是 一个 总的 的 第八 glbs 在 这

isplsi 2032e 设备. 各自 glb 是 制造 向上 的 四

macrocells. 各自 glb 有 18 输入, 一个 可编程序的

和/或者/独有的 或者 排列, 和 四 输出 这个 能

是 配置 至 是 也 combinatorial 或者 注册.

输入 至 这 glb 来到 从 这 grp 和 专心致志的

输入. 所有 的 这 glb 输出 是 brought 后面的 在 这

grp 所以 那 它们 能 是 连接 至 这 输入 的 任何

glb 在 这 设备.

这 设备 也 有 32 i/o cells, 各自 的 这个 是 直接地

连接 至 一个 i/o 管脚. 各自 i/o cell 能 是 individually