3.3v 零 延迟 缓存区

CY2304

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文档 #: 38-07247 rev. *c 修订 12月 7, 2002

特性

• 零 输入-输出 传播 延迟, 可调整的 用

电容的 加载 在 fbk 输入

• 多样的 配置 – 看 “available configura-

tions” 表格

• 多样的 低-skew 输出

— 输出-输出 skew 较少 比 200 ps

— 设备-设备 skew 较少 比 500 ps

• 10-mhz 至 133-mhz 运行 范围

• 低 jitter, 较少 比 200 ps 循环-循环

• 空间-节省 8-管脚 150-mil soic 包装

• 3.3v 运作

• 工业的 温度 有

函数的 描述

这 cy2304 是 一个 3.3v 零 延迟 缓存区 设计 至 distribute

高-速 clocks 在 pc, workstation, datacom, telecom, 和

其它 高-效能 产品.

这 部分 有 一个 在-碎片 阶段-锁 循环 (pll) 那 locks 至

一个 输入 时钟 提交 在 这 ref 管脚. 这 pll 反馈 是

必需的 至 是 驱动 在 这 fbk 管脚, 和 能 是 得到

从 一个 的 这 输出. 这 输入-至-输出 skew 是

有保证的 至 是 较少 比 250 ps, 和 输出-至-输出 skew

是 有保证的 至 是 较少 比 200 ps.

这 cy2304 有 二 banks 的 二 输出 各自.

这 cy2304 pll enters 一个 电源-向下 状态 当 那里 是

非 rising edges 在 这 ref 输入. 在 这个 模式, 所有 输出 是

三-陈述 和 这 pll 是 转变 止, 结果 在 较少 比

25

µ

一个 的 电流 绘制.

多样的 cy2304 设备 能 接受 这 一样 输入 时钟 和

distribute 它 在 一个 系统. 在 这个 情况, 这 skew 在 这

输出 的 二 设备 是 有保证的 至 是 较少 比 500 ps.

这 cy2304 是 有 在 二 不同的 配置, 作

显示 在 这

“

有 配置

”

表格. 这 cy2304

–

1

是 这 根基 部分, 在哪里 这 输出 发生率 equal 这

涉及 如果 那里 是 非 计数器 在 这 反馈 path.

这 cy2304

–

2 准许 这 用户 至 获得 ref 和 1/2x 或者 2x

发生率 在 各自 输出 bank. 这 精确的 配置 和

输出 发生率 取决于 在 这个 输出 驱动 这

反馈 管脚.

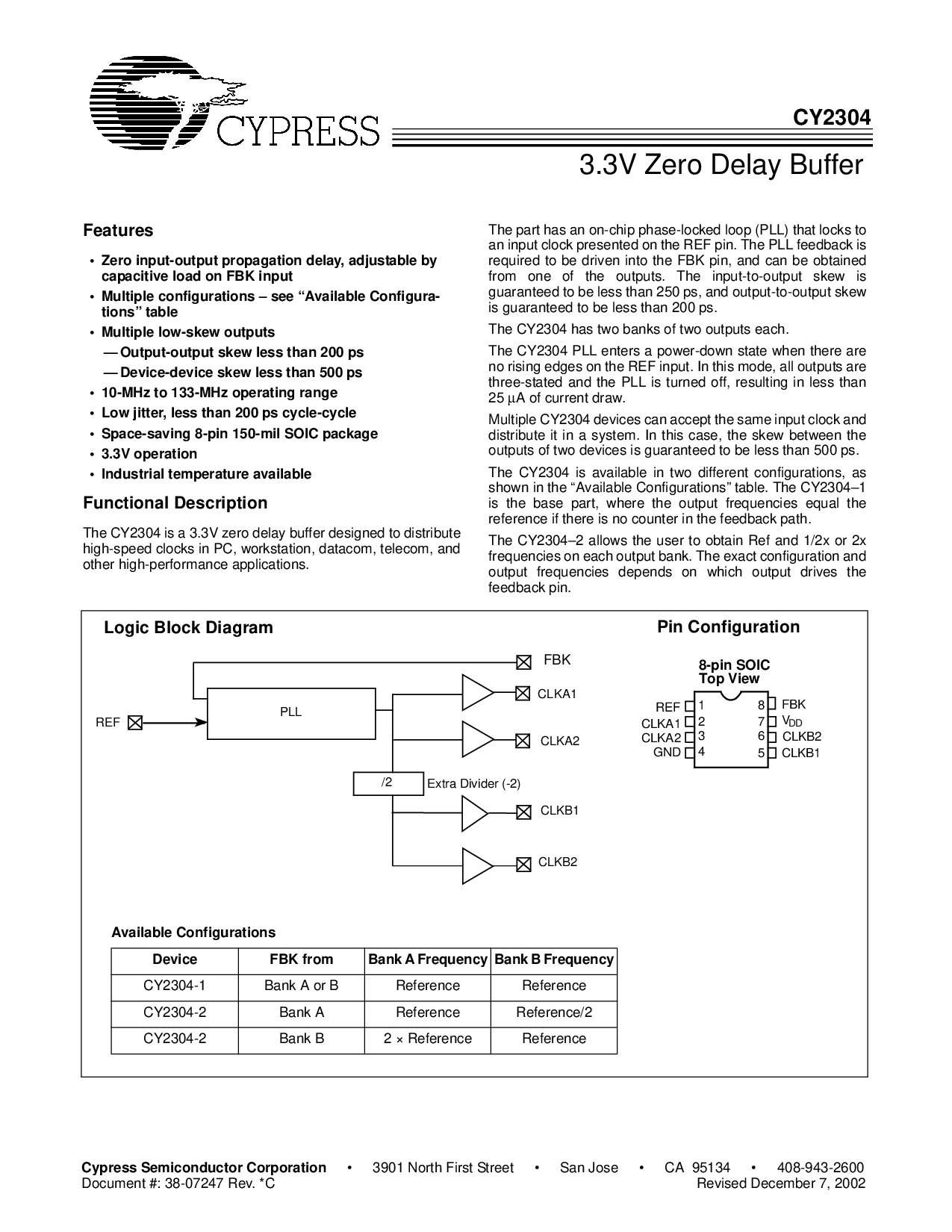

PLL

CLKA1

CLKA2

CLKB1

REF

CLKB2

/2

extra 分隔物 (-2)

逻辑 块 图解

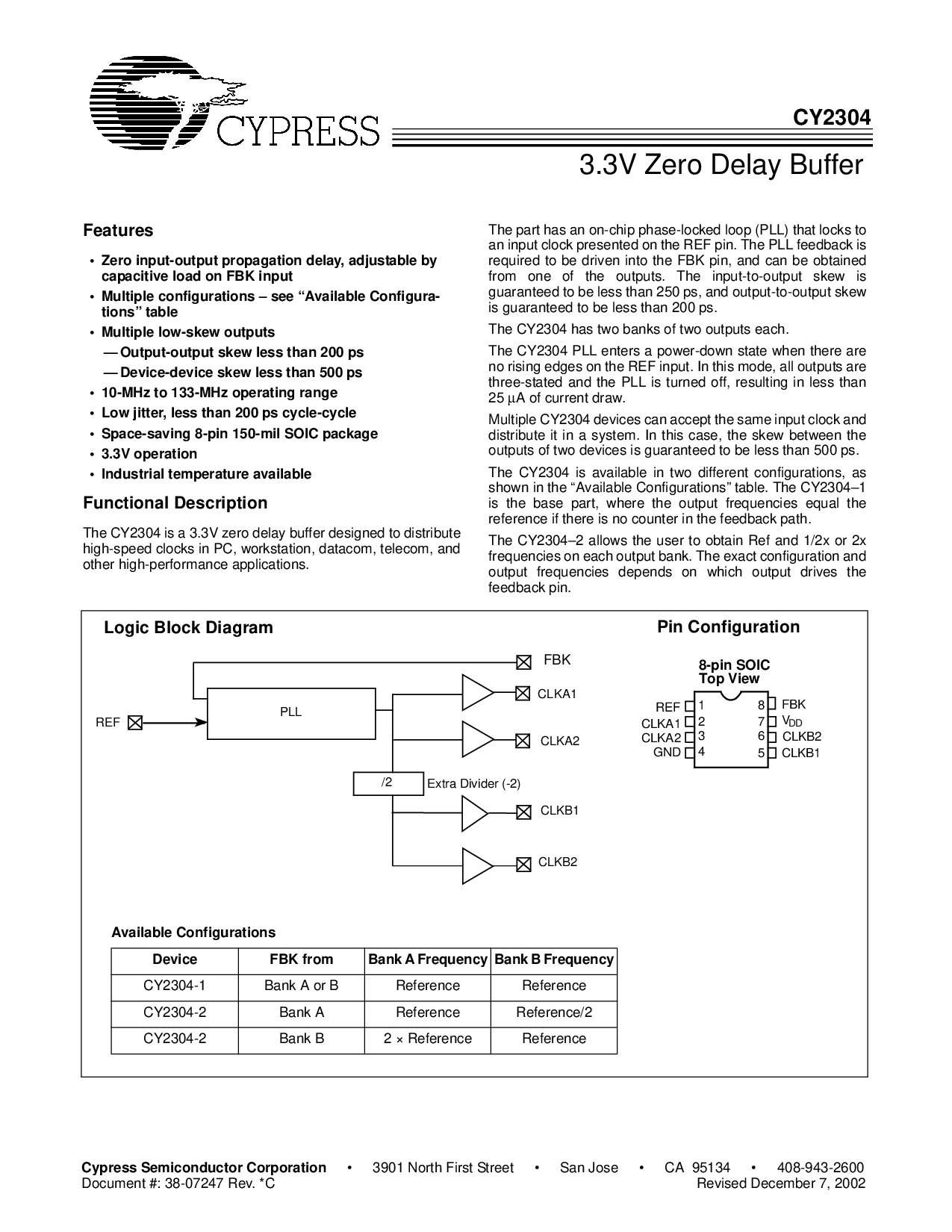

1

2

3

4

5

8

7

6

REF

CLKA1

CLKA2

地

V

DD

FBK

CLKB1

顶 视图

8-管脚 soic

管脚 配置

CLKB2

FBK

有 配置

设备 FBK从 bank 一个 频率 bank b 频率

cy2304-1 bank 一个 或者 b 涉及 涉及

cy2304-2 bank 一个 涉及 涉及/2

cy2304-2 bank b 2

×

涉及 涉及