4

LTC1448

clk (管脚 1):

串行 接口 时钟. 内部的 施密特 trig-

ger 在 这个 输入 准许 直接 optocoupler 接口.

D

在

(管脚 2):

串行 接口 数据. 数据 在 这 d

在

管脚 是

latched 在 这 变换 寄存器 在 这 rising 边缘 的 这 串行

时钟.

cs/ld (管脚 3):

串行 接口 使能 和 加载 控制.

当 cs/ld 是 低 这 clk 信号 是 使能, 所以 这 数据

能 是 clocked 在. 当 cs/ld 是 牵引的 高, 数据 是

承载 从 这 变换 寄存器 在 这 dac 寄存器,

PINFUNCTIONS

UUU

updating 这 dac 输出 和 这 clk 是 无能

内部.

ref (管脚 4):

涉及 输入 为 两个都 dacs. 这个 管脚 能

是 系 至 v

CC

. 这 输出 将 摆动 从 0v 至 ref. 这

典型 输入 阻抗 是 12.5k.

V

输出 一个

, v

输出 b

(管脚 5, 8):

缓冲 dac 输出.

地 (管脚 6):

地面.

V

CC

(管脚 7):

积极的 供应 输入. 2.7v

≤

V

CC

≤

5.5v.

需要 一个 绕过 电容 至 地面.

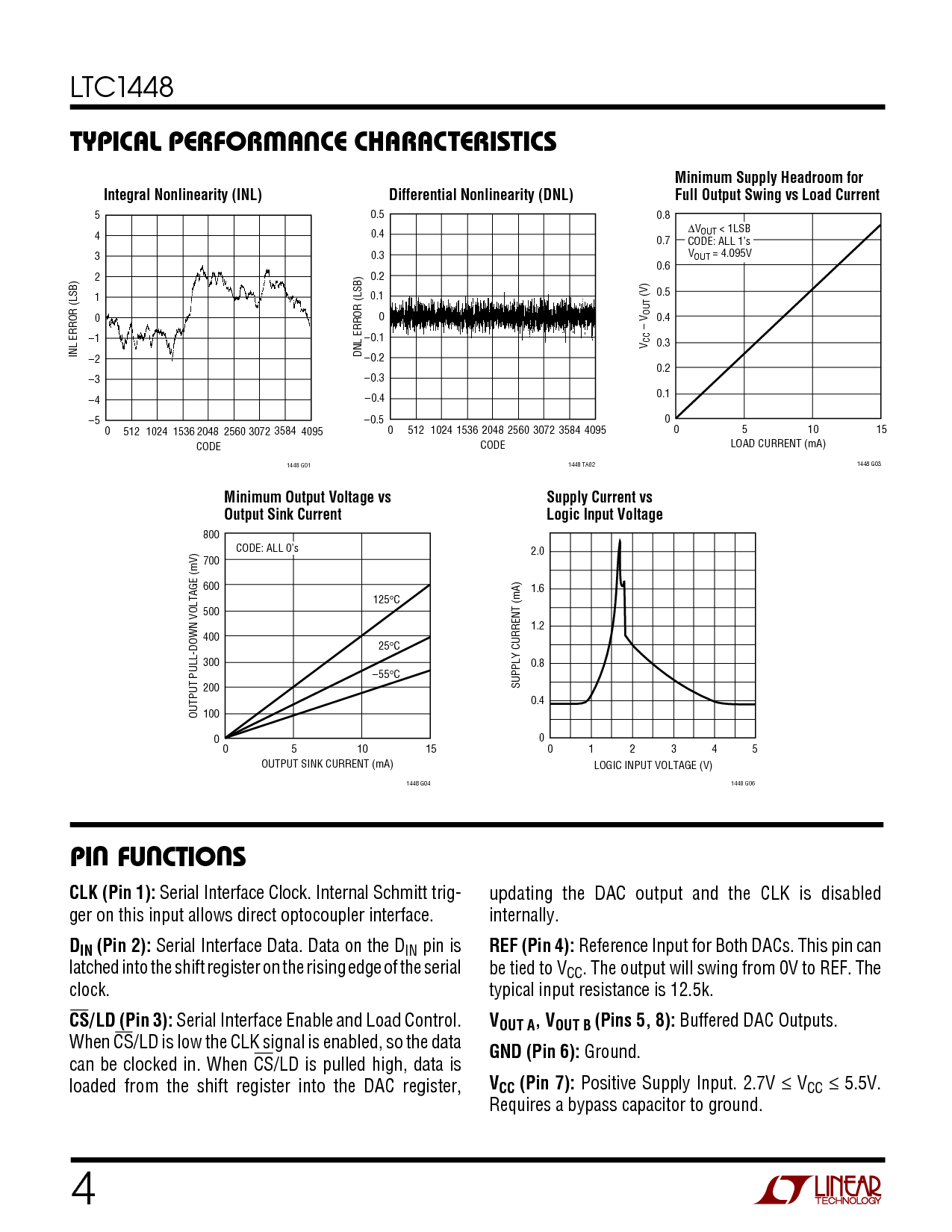

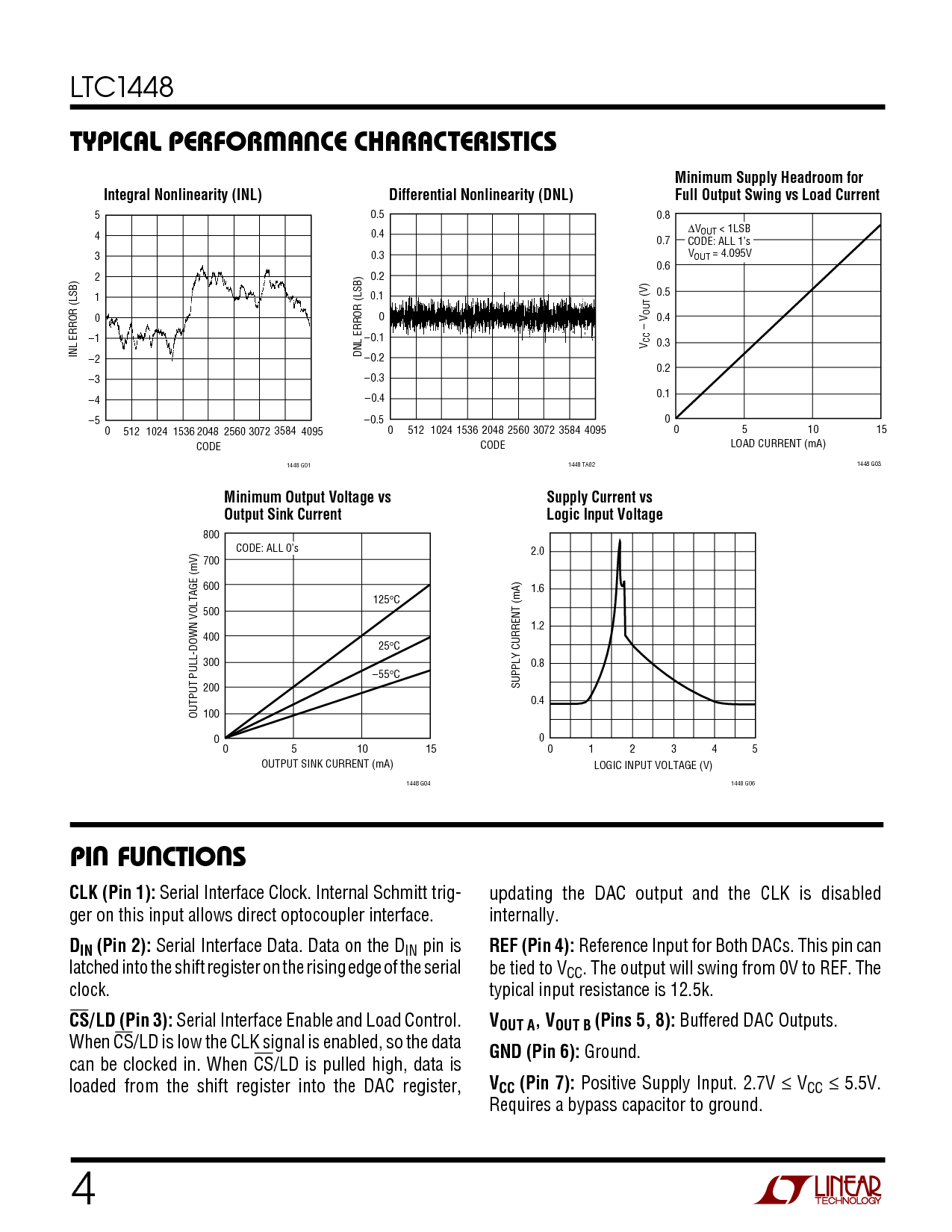

典型 perforM一个Nce characTERISTICS

UW

加载 电流 (毫安)

0

V

CC

– v

输出

(v)

51015

1448 g03

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

∆

V

输出

< 1lsb

代号: 所有 1’s

V

输出

= 4.095v

输出 下沉 电流 (毫安)

0

输出 拉-向下 电压 (mv)

51015

1448 g04

800

700

600

500

400

300

200

100

0

代号: 所有 0’s

125

°

C

25

°

C

–55

°

C

integral 非线性 (inl)

最小 供应 头上空间 为

全部 输出 摆动 vs 加载 电流

最小 输出 电压 vs

输出 下沉 电流

供应 电流 vs

逻辑 输入 电压

差别的 非线性 (dnl)

代号

0

inl 错误 (lsb)

5

4

3

2

1

0

–1

–2

–3

–4

–5

1024

2048

2560

1448 g01

512 1536

3072

3584

4095

代号

0

–0.5

dnl 错误 (lsb)

–0.4

–0.2

–0.1

0

0.5

0.2

1024 2048 2560

1448 ta02

–0.3

0.3

0.4

0.1

512 1536 3072 3584 4095

逻辑 输入 电压 (v)

0

供应 电流 (毫安)

2.0

1.6

1.2

0.8

0.4

0

4

1448 g06

1

2

3

5