ddr sdram

4gb 注册 dimm

Rev. 0.4 april. 2004

便条 :

1. vid 是 这 巨大 的 the 区别 在 这 输入 水平的 在 ck 和 这 输入 在 ck.

2. 这 值 的 v

IX

是 预期的 至 equal 0.5*v

DDQ

的 这 transmitting 设备 和 必须 追踪 变化 在 这 直流 水平的 的 这 一样.

3. 这些 参数 应当 是 测试在 这 pim 在 真实的 组件 和 将 是 checked 在 也 这 管脚 或者 这 垫子 在

simulation. 这 交流 和 直流 输入 specificatims 是 refation 至 一个 vref envelope 那 有 被 带宽 限制 20mhz.

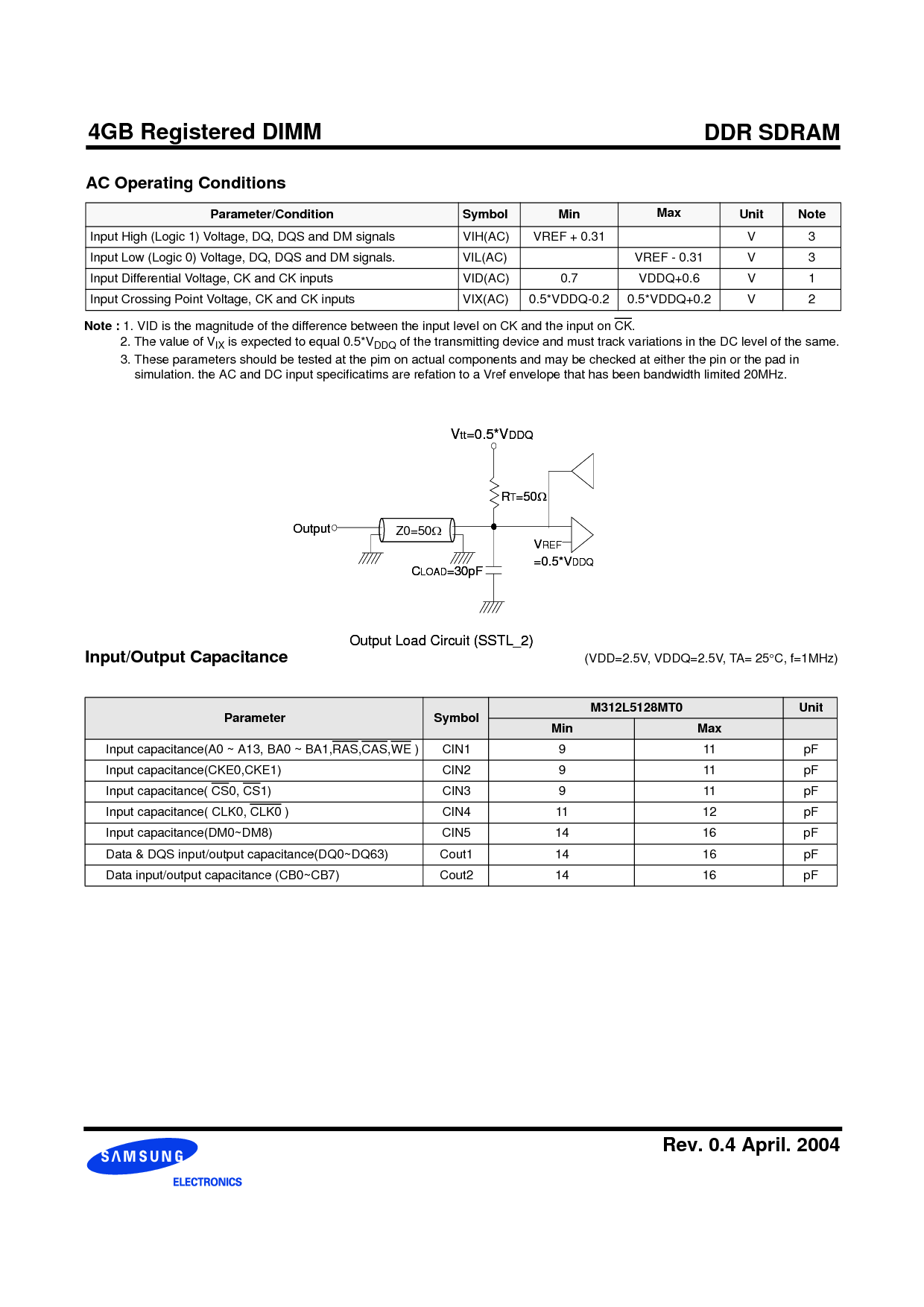

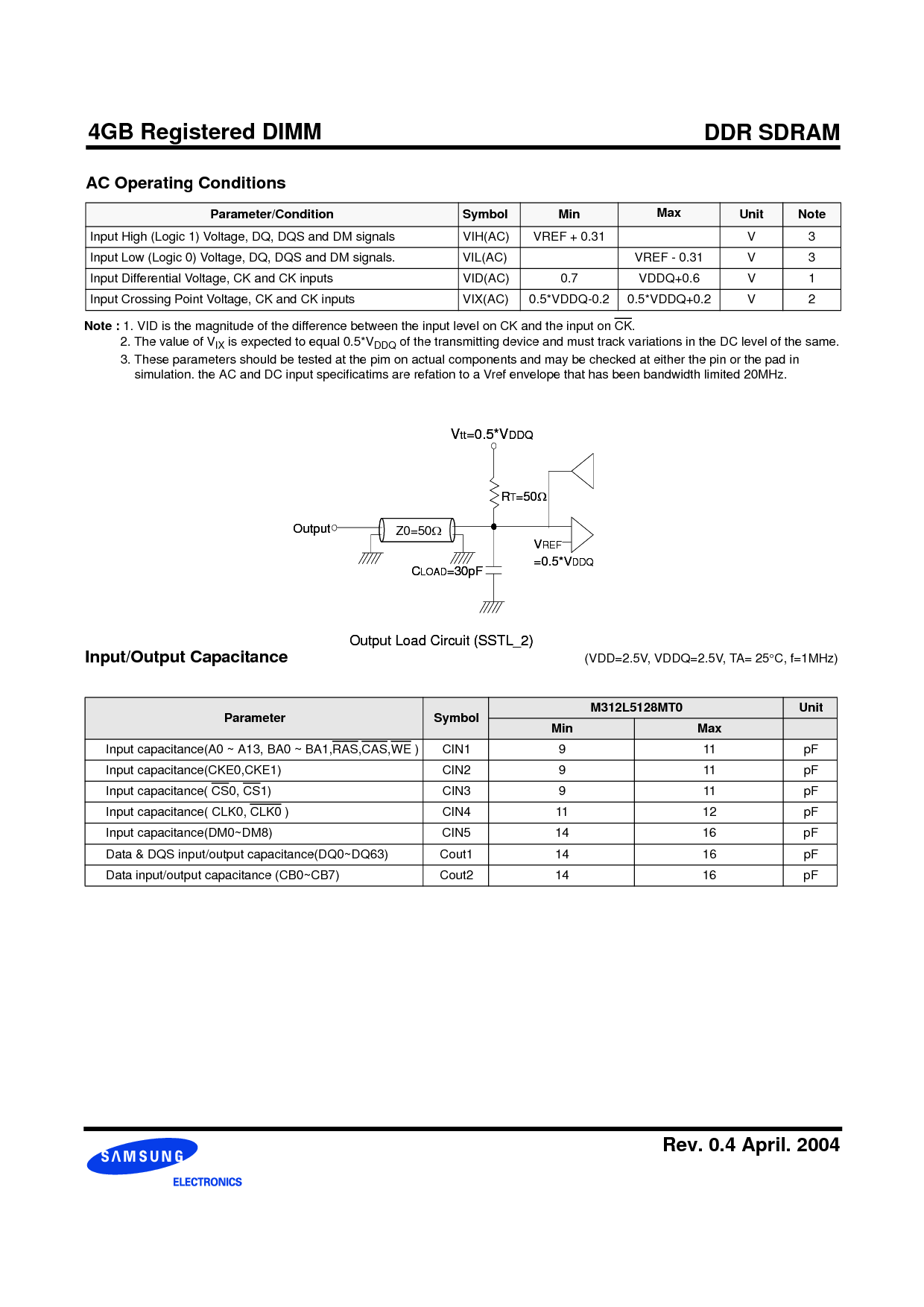

输出 加载 电路 (sstl_2)

输出

Z0=50

Ω

C

加载

=30pF

V

REF

=0.5*v

DDQ

R

T

=50

Ω

V

tt

=0.5*v

DDQ

输入/输出 电容

(vdd=2.5v, vddq=2.5v, ta= 25

°

c, f=1mhz)

参数 标识

M312L5128MT0 单位

最小值 最大值

输入 电容(a0 ~ a13, ba0 ~ ba1,ras,cas,我们)cin1 9 11 pF

输入 电容(cke0,cke1) CIN2 9 11 pF

输入 电容( cs

0, cs1) CIN3 9 11 pF

输入 电容( clk0, clk0

) CIN4 11 12 pF

输入 电容(dm0~dm8) CIN5 14 16 pF

数据 &放大; dqs 输入/输出 capacitance(dq0~dq63) Cout1 14 16 pF

数据 输入/输出 电容 (cb0~cb7) Cout2 14 16 pF

交流 运行 情况

参数/情况 标识 最小值

最大值

单位 便条

输入 高 (逻辑 1) 电压, dq, dqs 和 dm 信号 vih(交流) vref + 0.31 V 3

输入 低 (逻辑 0) 电压, dq, dqs 和 dm signals. vil(交流) vref - 0.31 V 3

输入 差别的 电压, ck 和 ck 输入 vid(交流) 0.7 vddq+0.6 V 1

输入 越过 要点 电压, ck 和 ck输入 vix(交流) 0.5*vddq-0.2 0.5*vddq+0.2 V 2

输出 加载 电路 (sstl_2)

输出

Z0=50

Ω

C

加载

=30pF

V

REF

=0.5*v

DDQ

R

T

=50

Ω

V

tt

=0.5*v

DDQ