motorola cmos 逻辑 数据

21

MC14001UB

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

切换 characteristics*

(c

L

= 50 pf, t

一个

= 25

_

c)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

典型的

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

标识

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

V

DD

Vdc

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

最小值

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

典型值 #

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

最大值

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

单位

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

输出 上升 时间

t

TLH

= (3.0 ns/pf) c

L

+ 30 ns

t

TLH

= (1.5 ns/pf) c

L

+ 15 ns

t

TLH

= (1.1 ns/pf) c

L

+ 10 ns

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

t

TLH

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

5.0

10

15

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

—

—

—

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

180

90

65

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

360

180

130

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

输出 下降 时间

t

THL

= (1.5 ns/pf) c

L

+ 25 ns

t

THL

= (0.75 ns/pf) c

L

+ 12.5 ns

t

THL

= (0.55 ns/pf) c

L

+ 9.5 ns

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

t

THL

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

5.0

10

15

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

—

—

—

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

100

50

40

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

200

100

80

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

传播 延迟 时间

t

PLH

, t

PHL

= (1.7 ns/pf) c

L

+ 30 ns

t

PLH

, t

PHL

= (0.66 ns/pf) c

L

+ 22 ns

t

PLH

, t

PHL

= (0.50 ns/pf) c

L

+ 15 ns

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

t

PLH

, t

PHL

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

ÎÎÎÎÎ

5.0

10

15

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

—

—

—

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

90

50

40

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

180

100

80

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ÎÎÎ

ns

* 这 formulas 给 是 为 这 典型 特性 仅有的 在 25

_

c.

#data labelled “typ” 是 不 至 是 使用 为 设计 目的 但是 是 将 作 一个 indication 的 这 ic’s 潜在的 效能.

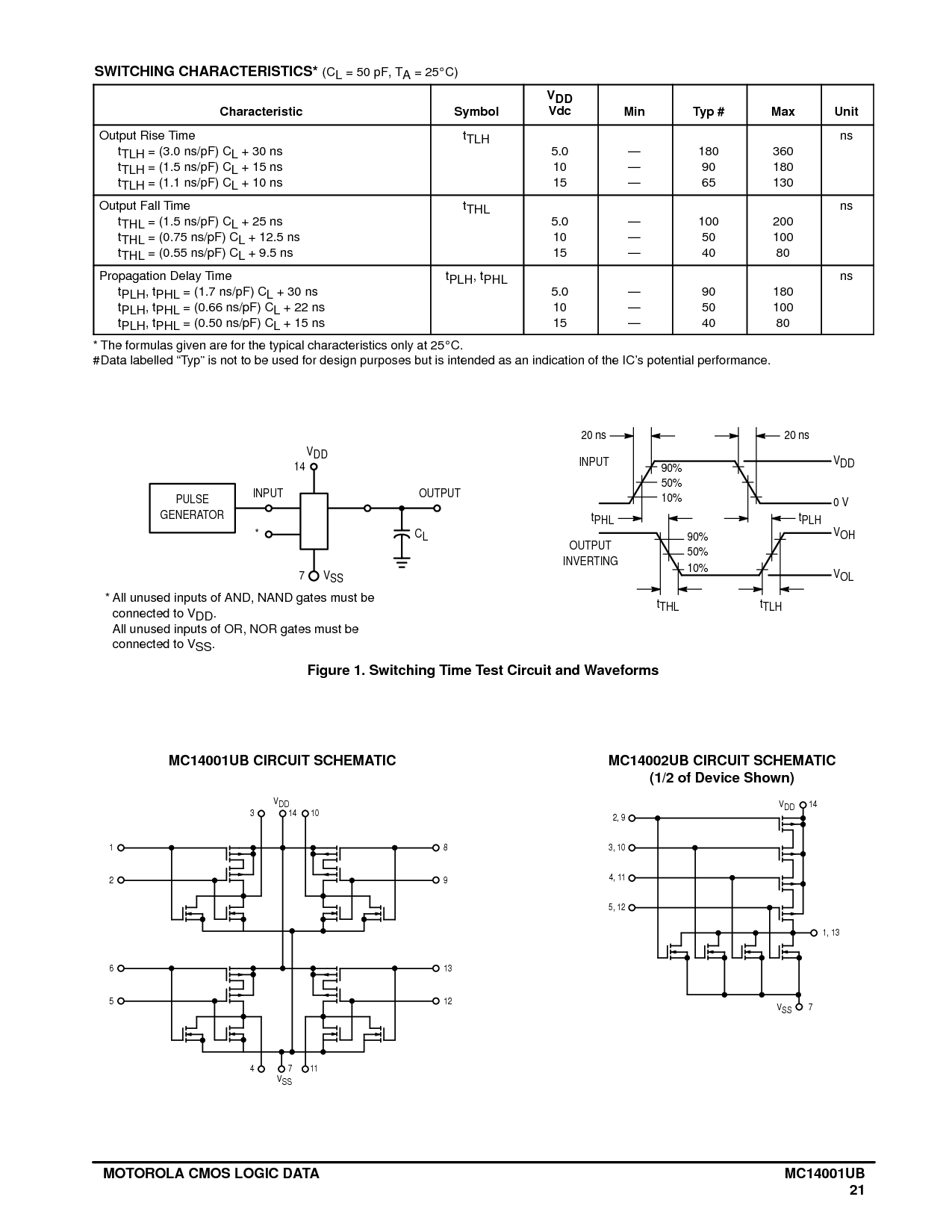

图示 1. 切换 时间 测试 电路 和 波形

V

DD

14

V

SS

输出

C

L

输入

*

7

脉冲波

发生器

20 ns 20 ns

输入

输出

反相的

t

PHL

t

PLH

90%

50%

10%

90%

50%

10%

t

THL

t

TLH

V

DD

0 v

V

OH

V

OL

* 所有 unused 输入 的 和, 与非 门 必须 是

连接 至 v

DD

.

所有 unused 输入 的 或者, 也不 门 必须 是

连接 至 v

SS

.

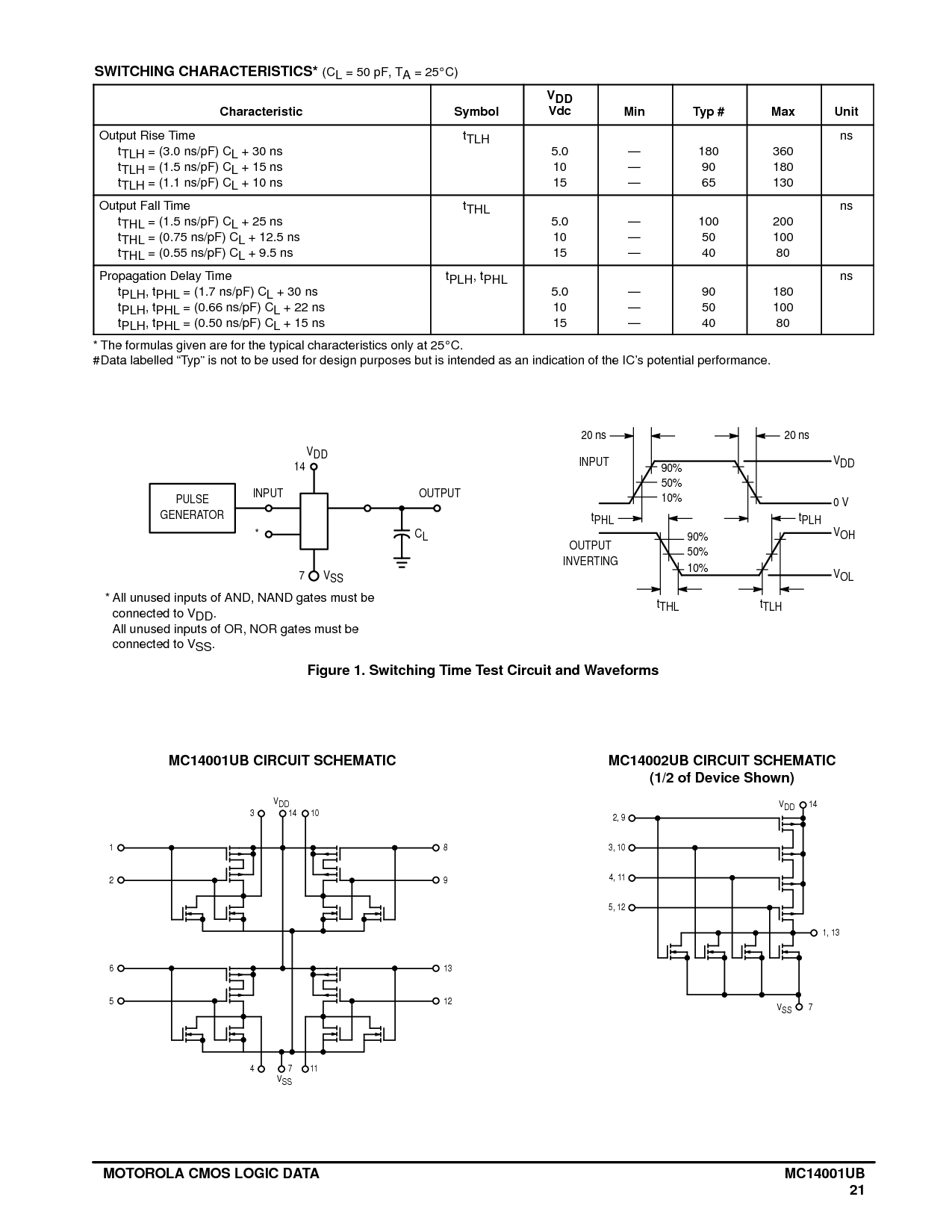

mc14001ub 电路 图式 mc14002ub 电路 图式

(1/2 的 设备 显示)

14 103

V

DD

6

5

2

1

V

SS

4 7 11

12

13

9

8

5, 12

4, 11

3, 10

2, 9

V

DD

14

1, 13

V

SS

7